Valere Versnip

Newbie level 4

Hello,

I'm wondering quite some time now if it is possible to check for same net clearances in altium designer?

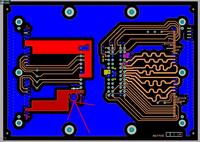

I often place groundfills on top and bottom (along with the routing). I give these polygons a big clearance, so they do not interfere with the controlled impedance of traces. Example --> see screenshot.

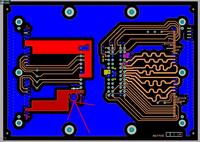

But: when I do this there are random places where the clearance between the groundfill polygon, and other same net objects are too small for manufacturing. Look at this screenshot (red oval is zoom in of previous screenshot):

So the big thing here is: if the pad touches the polygon (so if it is connected), there should not be an error. But if the pad doesn't touch the polygon, I should be able to create an error if the clearance is smaller than the default clearance.

I have tried with the queries, but I cannot get it right.

Difficult explanation for somthing simple

Any suggestions?

PS: I also use Allegro, and this has a same net drc that creates errors when this happens...

Thx

I'm wondering quite some time now if it is possible to check for same net clearances in altium designer?

I often place groundfills on top and bottom (along with the routing). I give these polygons a big clearance, so they do not interfere with the controlled impedance of traces. Example --> see screenshot.

But: when I do this there are random places where the clearance between the groundfill polygon, and other same net objects are too small for manufacturing. Look at this screenshot (red oval is zoom in of previous screenshot):

So the big thing here is: if the pad touches the polygon (so if it is connected), there should not be an error. But if the pad doesn't touch the polygon, I should be able to create an error if the clearance is smaller than the default clearance.

I have tried with the queries, but I cannot get it right.

Difficult explanation for somthing simple

Any suggestions?

PS: I also use Allegro, and this has a same net drc that creates errors when this happens...

Thx