shiva_107

Newbie level 4

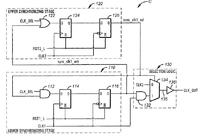

You have two clocks, CLK1, CLK2 goes as inputs to a MUX, you have a select line. The output of this mux goes to the clk of flip flop.

What additional circuit you should add such that if you switch from one clock to another you should not see any glitches.

____ ____

CLK1 - ___| |____| |____

____ ____

CLK2- _| |___| |____

_________________

sel - ____|

sel 0 selects clk1, sel 1 selects clk2...in this case you will see a glitch.

What additional circuit you should add such that if you switch from one clock to another you should not see any glitches.

____ ____

CLK1 - ___| |____| |____

____ ____

CLK2- _| |___| |____

_________________

sel - ____|

sel 0 selects clk1, sel 1 selects clk2...in this case you will see a glitch.