Monady

Advanced Member level 4

SR Problem

Hi dear all friends

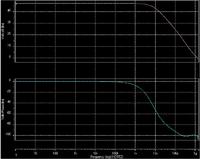

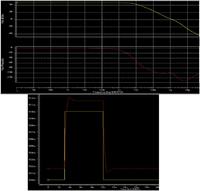

I used of folded cascode opamp as unity gain buffer, this circuit designed for Slew Rate greater than 2.5*10^9 V/S (due to the 0.5V variation in 0.2ns). after simulation, I(M11) was 1mA with 0.3pF capacitance load, and it means: SR=1mA/0.3pF= 3.33*10^9 V/S. I really mixed up because as you can see in the attached pic, output settle in more than 2ns although SR is reasonable .

I would be appreciated for any help.

P.s. pen loop UGBW is higher than 1GHz, Phase margin=80degree

pen loop UGBW is higher than 1GHz, Phase margin=80degree

Hi dear all friends

I used of folded cascode opamp as unity gain buffer, this circuit designed for Slew Rate greater than 2.5*10^9 V/S (due to the 0.5V variation in 0.2ns). after simulation, I(M11) was 1mA with 0.3pF capacitance load, and it means: SR=1mA/0.3pF= 3.33*10^9 V/S. I really mixed up because as you can see in the attached pic, output settle in more than 2ns although SR is reasonable .

I would be appreciated for any help.

P.s.