hmsheng

Full Member level 4

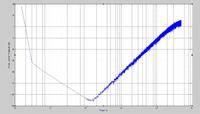

dither dsm

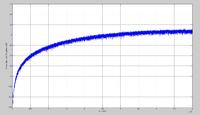

It's known that a spur free fractional-N frequency synthesizer is mostly realized with a sigma-delta modulator and a multi-module divider. The control bits of the multi-module divider is dithered by the sigma-delta modulator (SDM). But the output of the SDM is a cyclic data series. If the accumulator has m bits, then the output of SDM will repeat after 2^(m+1) clock cycle for a 3rd order SDM. A cyclic control bits for the multi-module divider will cause spur. So, why said it's spur free?

It's known that a spur free fractional-N frequency synthesizer is mostly realized with a sigma-delta modulator and a multi-module divider. The control bits of the multi-module divider is dithered by the sigma-delta modulator (SDM). But the output of the SDM is a cyclic data series. If the accumulator has m bits, then the output of SDM will repeat after 2^(m+1) clock cycle for a 3rd order SDM. A cyclic control bits for the multi-module divider will cause spur. So, why said it's spur free?