wtr

Full Member level 5

I've read the following thread.

https://www.edaboard.com/threads/295879/

I can successfully assign something like the following (in concurrent part of architecture)

however the following

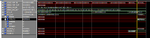

just gives me a glitch see attached picture

Also having problems with alias's

modelsim gives

** Error: (vsim-8523) Cannot reference the signal "/scp0466b1_tb/FPGA/PADDR_S" before it has been elaborated.

from verror -all log

https://www.edaboard.com/threads/295879/

I can successfully assign something like the following (in concurrent part of architecture)

Code VHDL - [expand]

however the following

Code VHDL - [expand]

just gives me a glitch see attached picture

Also having problems with alias's

Code VHDL - [expand]

modelsim gives

** Error: (vsim-8523) Cannot reference the signal "/scp0466b1_tb/FPGA/PADDR_S" before it has been elaborated.

from verror -all log

What am I doing wrong? Can't force concurrents apparently. Also does anyone have access to these sections of standard?vsim Message # 8523:

A signal must have been elaborated before it can be referenced in an

external name.

The default value for the type of the signal has been used.

[DOC: IEEE Std 1076-2008 VHDL LRM - 8.7 External names]

[DOC: IEEE Std 1076-2008 VHDL LRM - 14.2 Elaboration of a design hierarchy]

Last edited: