neazoi

Advanced Member level 6

Hi,

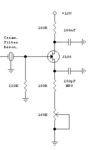

This little crystal oscillator I have designed by trial and error, uses crystals or ceramic resonators to oscillate at HF.

There ia a "hitten" capacitor formed by the internal capacitance of the gate-source of the FET.

When I set the source trimmer at extreme ends (especially at low values, max OSC gain) the oscillator changes frequency by a few 100's Hz.

I have noticed this with ceramic resonators as well as with crystals and also even when I have put a real NP0 capacitor between the gate-source.

Why is this hapenning?

What can I do to correct this, without sacrificing too much the range of the gain of the oscillator?

This little crystal oscillator I have designed by trial and error, uses crystals or ceramic resonators to oscillate at HF.

There ia a "hitten" capacitor formed by the internal capacitance of the gate-source of the FET.

When I set the source trimmer at extreme ends (especially at low values, max OSC gain) the oscillator changes frequency by a few 100's Hz.

I have noticed this with ceramic resonators as well as with crystals and also even when I have put a real NP0 capacitor between the gate-source.

Why is this hapenning?

What can I do to correct this, without sacrificing too much the range of the gain of the oscillator?