cooldude_1986

Newbie level 4

Please help me with this question

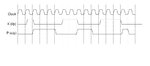

Given the following waveform what would be the structure that is needed to generate this.

What is the general approach to these kinda problems.

Thank you

Given the following waveform what would be the structure that is needed to generate this.

What is the general approach to these kinda problems.

Thank you

Use proper titles in your posts relevant to the content of your question, next time your post will be deleted [alexan_e]