bhl777

Full Member level 6

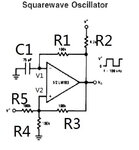

Hello everyone, this is a simple question of the application of square wave generator using LM393 comparator. I am still a little bit confuces of how it works.

(1)Could you have a look at the attachment to tell me the detailed analysis steps of it?

Since now I only know that V1 is a sawtooth wave and V2 is like a DC. But do not know how the feedback resistors work.

(2)At the mean time, could you tell me how to calculate the cycle of the output? Someone in the internet said it is like 1.1RC but I do not know how to figure it out.

Thank you so much!

(1)Could you have a look at the attachment to tell me the detailed analysis steps of it?

Since now I only know that V1 is a sawtooth wave and V2 is like a DC. But do not know how the feedback resistors work.

(2)At the mean time, could you tell me how to calculate the cycle of the output? Someone in the internet said it is like 1.1RC but I do not know how to figure it out.

Thank you so much!