otis

Member level 3

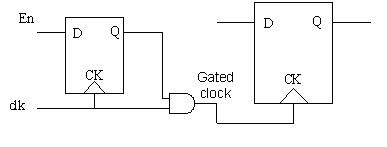

clock gating

I am going to add a clock gate in my design. There are many papers in the Internet says do not use clock gate logic directly instead use ICG - Integrated Clock Gate.

But I dont know how to do this in RTL level.

I found this cell in the technology library.

But I am not sure how can I use this cell directly in RTL level.

I am going to add a clock gate in my design. There are many papers in the Internet says do not use clock gate logic directly instead use ICG - Integrated Clock Gate.

But I dont know how to do this in RTL level.

I found this cell in the technology library.

But I am not sure how can I use this cell directly in RTL level.

Last edited: