bhanu.somisetty

Newbie level 6

Hi All...

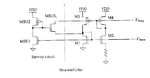

In the attachment,the startup circuit is used to avoid a condition "where the gate voltages of transistor M1,M2 become zero and M3,M4 become VDD and the circuit doesnt work".

Can anyone explain,why the gate voltages of M1,M2 go to zero and M3,M4 go to VDD?

Thanks a lot....

In the attachment,the startup circuit is used to avoid a condition "where the gate voltages of transistor M1,M2 become zero and M3,M4 become VDD and the circuit doesnt work".

Can anyone explain,why the gate voltages of M1,M2 go to zero and M3,M4 go to VDD?

Thanks a lot....