maxwell232

Newbie level 3

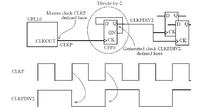

(1) generated clock

(2) multiple clock

(3) ideal clock

(4) propagated clock

i am really confused by them, would you tell me what the difference is between them?

thanks a lot

Added after 4 minutes:

by the way, if i want to understand those concepts clearly, what should i learn? STA, CTS or other things? would you give me some advice?

(2) multiple clock

(3) ideal clock

(4) propagated clock

i am really confused by them, would you tell me what the difference is between them?

thanks a lot

Added after 4 minutes:

by the way, if i want to understand those concepts clearly, what should i learn? STA, CTS or other things? would you give me some advice?