bharatsmile2007

Full Member level 3

Hi all,

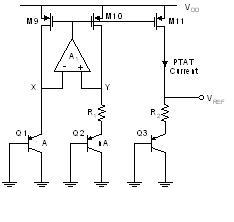

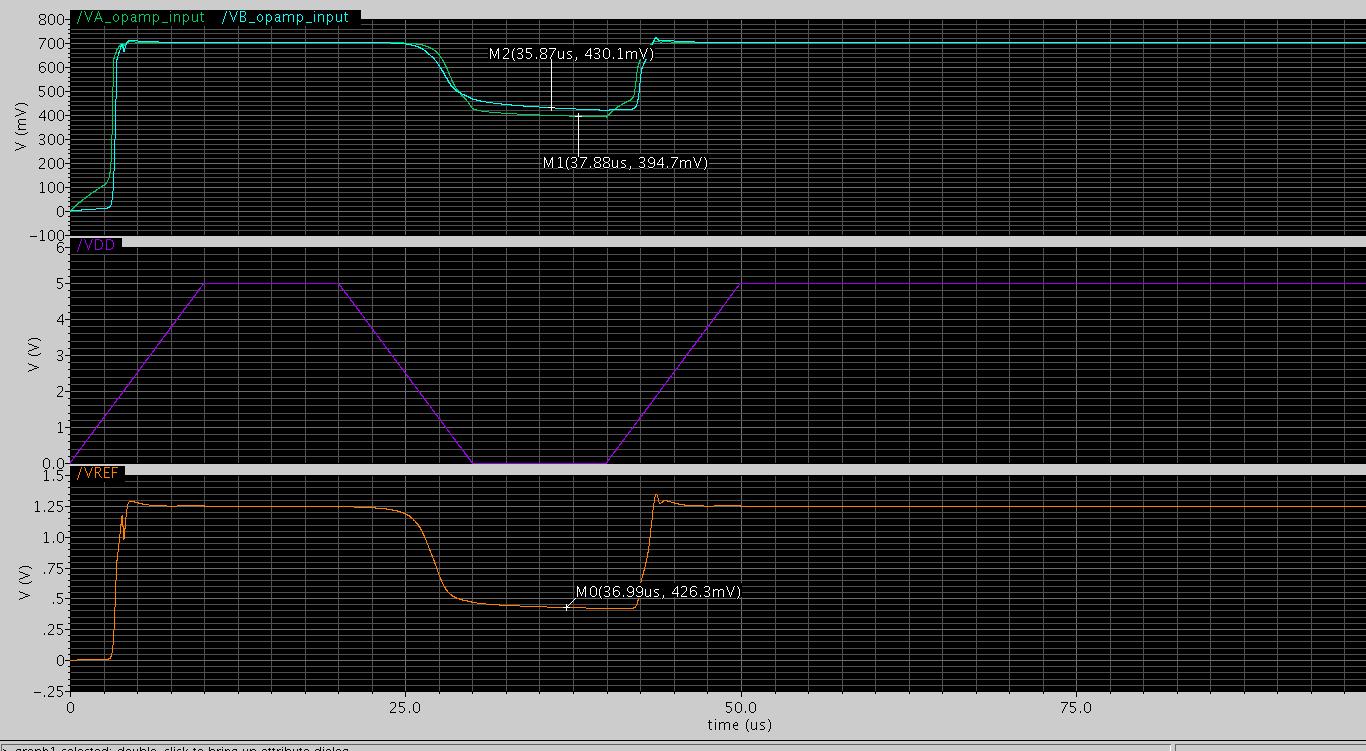

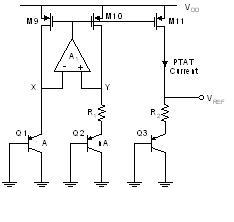

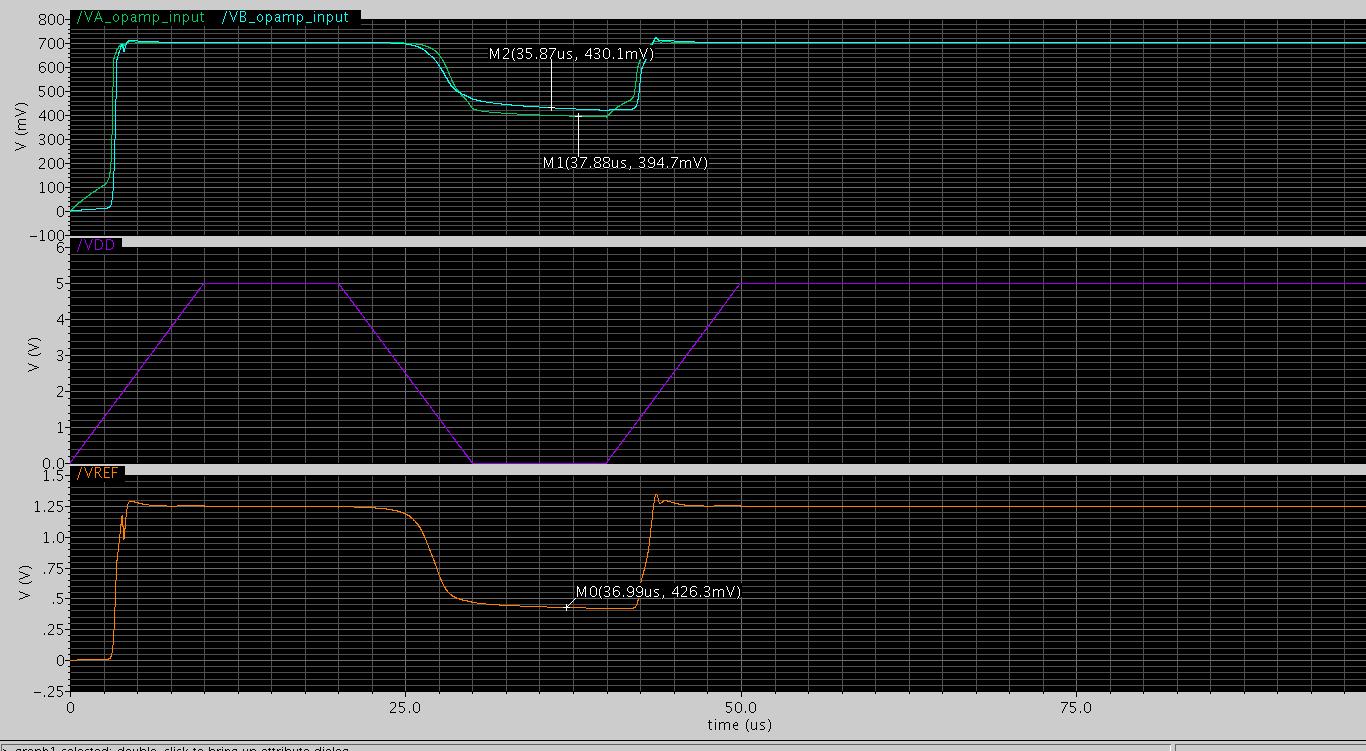

In a BGR.when given a pwl to vdd,varying from 5V to 0V.

when vdd is 5V Vref (output) is 1.26V,

when vdd is zero Vref is around 0.5V.

Can any one let me know what would be the possible reason for Vref not settling to zero volts?

pwl was given a rise/fall delay 10u and pulse width 10u...

Thanks

In a BGR.when given a pwl to vdd,varying from 5V to 0V.

when vdd is 5V Vref (output) is 1.26V,

when vdd is zero Vref is around 0.5V.

Can any one let me know what would be the possible reason for Vref not settling to zero volts?

pwl was given a rise/fall delay 10u and pulse width 10u...

Thanks