Follow along with the video below to see how to install our site as a web app on your home screen.

Note: This feature may not be available in some browsers.

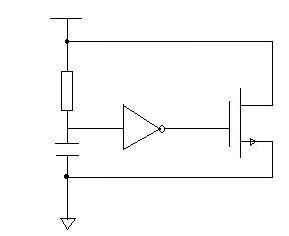

kenddo said:hi all, can anyone tell me what the ckt is posted below? i've seen it many times in different project . thanks