lty

Junior Member level 3

I am studying the ATPG recently.

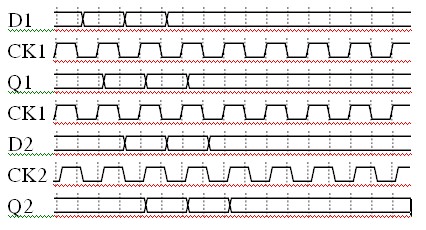

I try to understand why insert a look-up latch in a chain when the chain is crossing clock domain.

Can anybody give some answer about this, or give some reference?

I try to understand why insert a look-up latch in a chain when the chain is crossing clock domain.

Can anybody give some answer about this, or give some reference?