cupoftea

Advanced Member level 5

Hi,

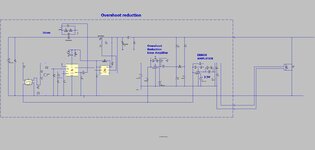

Would you agree, the attached is the De Facto method of eradicating overshoot in SMPS’s? As you know, opto-coupled SMPS’s have a slow bandwidth, and tend to suffer vout overshoot as a result. The attached is the best way to get rid of this, would you agree?

Simply using a 2nd error amp, set for a slightly higher vout than nominal, and with a slow start network, which of course, is "out of circuit", after whatever transient occurred has finished.

LTspice and jpeg attached.

Would you agree, the attached is the De Facto method of eradicating overshoot in SMPS’s? As you know, opto-coupled SMPS’s have a slow bandwidth, and tend to suffer vout overshoot as a result. The attached is the best way to get rid of this, would you agree?

Simply using a 2nd error amp, set for a slightly higher vout than nominal, and with a slow start network, which of course, is "out of circuit", after whatever transient occurred has finished.

LTspice and jpeg attached.