neazoi

Advanced Member level 6

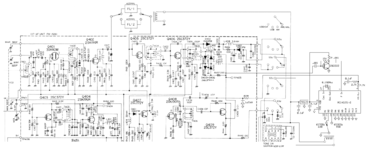

I am trying to lock the BFO of the FRG-7 (Yaesu) and the design is shown attached.

Whereas it locks fine, The audio tones are distorted (ringing). This happens on higher level signals not on lower.

This is shown in this video

The same ringing happens when I switch from USB to LSB and vice versa, for 1 second.

I noticed when I changed the loop capacitor on pin 4 of the PLL to higher value, the ringing becomes of lower frequency.

I do not know what is going on, any help?

Whereas it locks fine, The audio tones are distorted (ringing). This happens on higher level signals not on lower.

This is shown in this video

I noticed when I changed the loop capacitor on pin 4 of the PLL to higher value, the ringing becomes of lower frequency.

I do not know what is going on, any help?