VictorWu

Newbie level 5

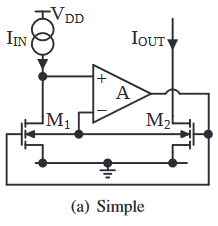

The author of the paper Wide Current Range and High Compliance-Voltage Bulk-Driven Current Mirrors: Simple and Cascode wrote that “Concerning the output transistor M2, if the output voltage (drain of M2) rises, the output current starts to increase. As a result, bulk of M2 (also M1) increases which in turn makes the gate voltage to decrease, the output current then decrease to the original value.”

I don't know why. I would really appreciate it if someone could explain it for me!

I don't know why. I would really appreciate it if someone could explain it for me!