Shishira

Junior Member level 2

- Joined

- Jun 8, 2018

- Messages

- 20

- Helped

- 0

- Reputation

- 0

- Reaction score

- 0

- Trophy points

- 1

- Location

- Dresden, Germany

- Activity points

- 228

Hi All,

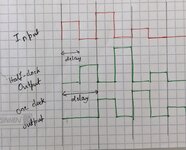

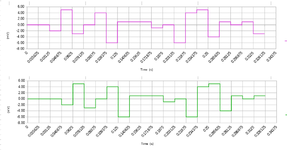

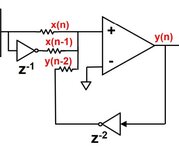

I want to introduce a delay of half and one clock period in an analog circuit. I need an element/circuit that can produce half-clock period in real circuit to be taped out. I cannot use a D flip flop as the output needed is an amplitude varying square signal. (atch 2). Looking forward to ideas..

I want to introduce a delay of half and one clock period in an analog circuit. I need an element/circuit that can produce half-clock period in real circuit to be taped out. I cannot use a D flip flop as the output needed is an amplitude varying square signal. (atch 2). Looking forward to ideas..