mike buba

Member level 2

Hi all,

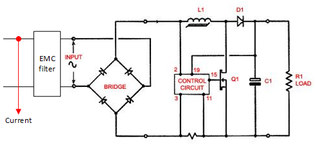

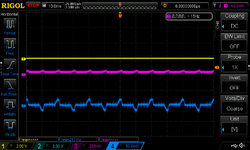

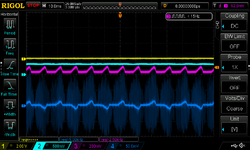

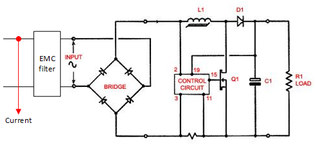

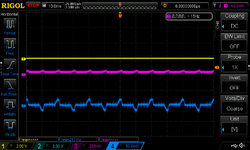

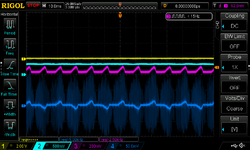

I am building an Active PFC circuit (Vin = 230 Vac, Vout = 700 Vdc, Pout = 4 kW) and I am noticing noise when the switch Q1 on the figure is on. One can assume the noise is visible on the oscilloscope because of the Ch4 current clamp poor filtering since I am also using another clamp to measure a DC current (Ch3) and there is no noise. Ch4 (blue) is input grid current, Ch3 (purple) is inductor L1 current. There is also an EMC filter Shaffner FN2030-30-08 at the input.

But when I compare two similar cases (same input voltage and power) with Q1 turned off and on, the noise is there, so the Ch4 probe, because of low filtering, just amplifies it.

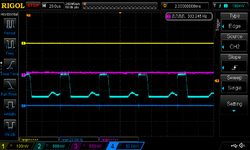

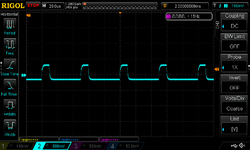

Switch Q1 turned off

Switch Q1 turned on

(Vout = 60 Vdc, Iout = 0.2 Adc)

(Vout = 60 Vdc, Iout = 0.2 Adc)

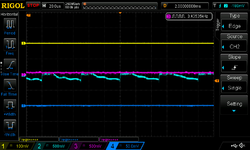

Switch Q1 turned on

(Vout = 350Vdc, Iout = 1.7 Adc)

(Vout = 350Vdc, Iout = 1.7 Adc)

I measure 6.6 kHz and 34.8 kHz spikes. Q1 switching frequency is 20 kHz.

I was trying hovering the current probe at the same distance from the converter above the components to try to see if there is a place with the 'bigger' noise, but I cannot see the change in the amplitude or intensity.

Are there any ways to reduce the overall noise in the converter?

I suspect the increased amount of noise is later affecting serial communication which breaks down at higher powers and voltages.

I am building an Active PFC circuit (Vin = 230 Vac, Vout = 700 Vdc, Pout = 4 kW) and I am noticing noise when the switch Q1 on the figure is on. One can assume the noise is visible on the oscilloscope because of the Ch4 current clamp poor filtering since I am also using another clamp to measure a DC current (Ch3) and there is no noise. Ch4 (blue) is input grid current, Ch3 (purple) is inductor L1 current. There is also an EMC filter Shaffner FN2030-30-08 at the input.

But when I compare two similar cases (same input voltage and power) with Q1 turned off and on, the noise is there, so the Ch4 probe, because of low filtering, just amplifies it.

Switch Q1 turned off

Switch Q1 turned on

(Vout = 60 Vdc, Iout = 0.2 Adc)

(Vout = 60 Vdc, Iout = 0.2 Adc)Switch Q1 turned on

(Vout = 350Vdc, Iout = 1.7 Adc)

(Vout = 350Vdc, Iout = 1.7 Adc)I measure 6.6 kHz and 34.8 kHz spikes. Q1 switching frequency is 20 kHz.

I was trying hovering the current probe at the same distance from the converter above the components to try to see if there is a place with the 'bigger' noise, but I cannot see the change in the amplitude or intensity.

Are there any ways to reduce the overall noise in the converter?

I suspect the increased amount of noise is later affecting serial communication which breaks down at higher powers and voltages.

Last edited: