MSAKARIM

Full Member level 3

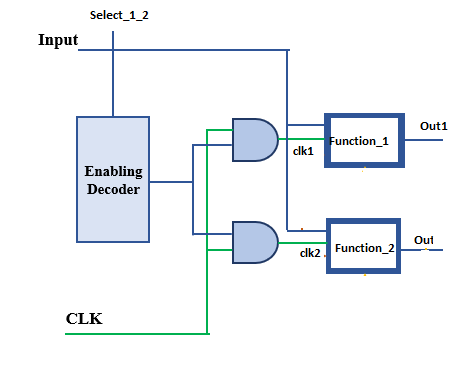

I have two functions that work with the same input data as shown in the figure. They aren't needed at the same time, so I need to clock only the required function to save calculations and power by the not used one. I used a decoder with AND gates to create sub-clocks for each function. Is this method effective in hardware implementation ? is my thought is right?