r.mirtaji

Junior Member level 3

Dear friends,

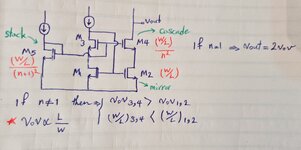

The following figure is the wide swing cascade current mirror

Why in design the ratio of \[ (W/L)3,4 \]is usually considered smaller than the ratio of \[ (W/L)1,2 \]

we know that \[ VoV↓ ∝ (L↓)/(W↑) ↓ \]

then Vov3,4 > Vov1,2 for example Vov1,2= .14v and Vov3,4=. 2v

Why don’t designer set the value of Vov equal for all transistors in the design?

The following figure is the wide swing cascade current mirror

Why in design the ratio of \[ (W/L)3,4 \]is usually considered smaller than the ratio of \[ (W/L)1,2 \]

we know that \[ VoV↓ ∝ (L↓)/(W↑) ↓ \]

then Vov3,4 > Vov1,2 for example Vov1,2= .14v and Vov3,4=. 2v

Why don’t designer set the value of Vov equal for all transistors in the design?