kaz1

Full Member level 6

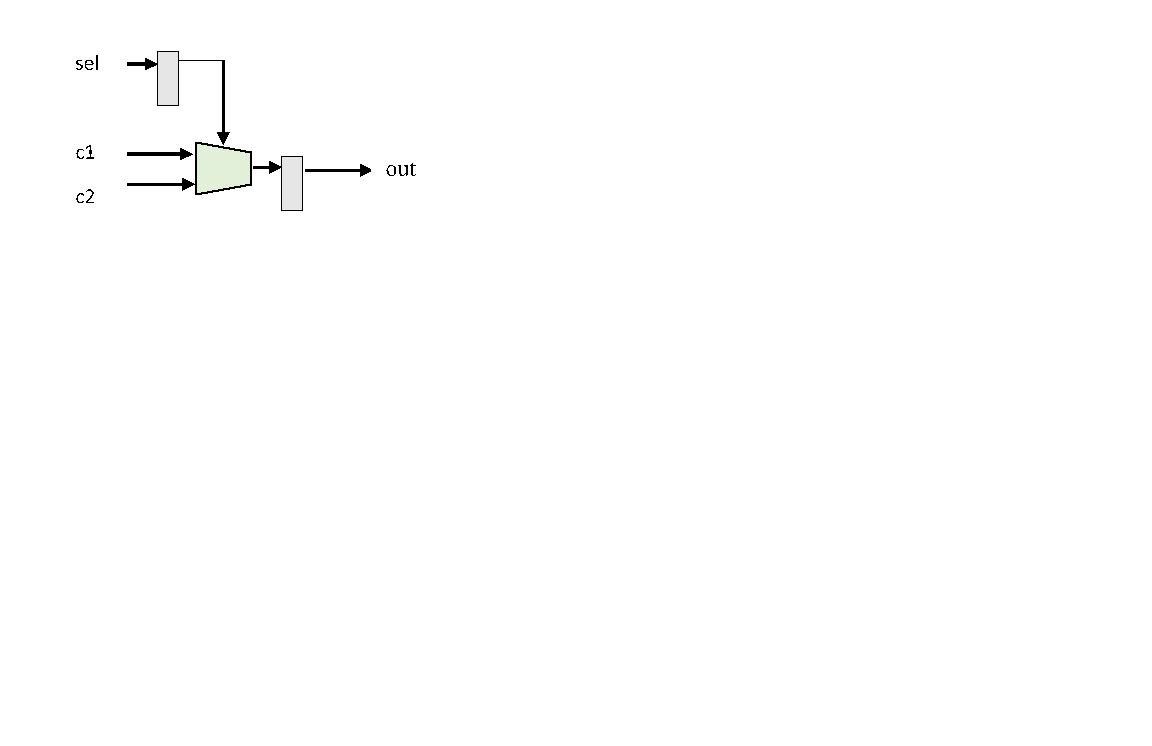

c1 and c2 are constants (wires).

sel selects one of them for output(out). There is timing path from sel register to out register but none from c1/c2 to out

How does Quartus or Vivado check the c1/c2 to out path since it is not a timing path by definition:

.

sel selects one of them for output(out). There is timing path from sel register to out register but none from c1/c2 to out

How does Quartus or Vivado check the c1/c2 to out path since it is not a timing path by definition:

.