renti

Newbie level 6

I have read some related posts in this forum, and changed the VNTOL,ABSTOL,ITL1, but it still didn't work yet,

I felt that it was the issure about the GND, the OP, but I don't know what to do .

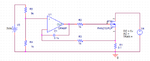

The circuit here is a DC load, which mainly consist of a MOSFET, a shunt resister, an OP amplifier.

When I did the simulation in PSPICS(orcad 9.2), it gave out the following message:

===============================================

I felt that it was the issure about the GND, the OP, but I don't know what to do .

The circuit here is a DC load, which mainly consist of a MOSFET, a shunt resister, an OP amplifier.

When I did the simulation in PSPICS(orcad 9.2), it gave out the following message:

===============================================

** Creating circuit file "test3-schematic1-test3.sim.cir"

** WARNING: THIS AUTOMATICALLY GENERATED FILE MAY BE OVERWRITTEN BY SUBSEQUENT SIMULATIONS

*Libraries:

* Local Libraries :

* From [PSPICE NETLIST] section of C:\Program Files\Orcad\PSpice\PSpice.ini file:

.lib "nom.lib"

*Analysis directives:

.TRAN 0 1000ms 0

.OPTIONS STEPGMIN

.OPTIONS ABSTOL= 1.0n

.OPTIONS ITL1= 500

.OPTIONS ITL4= 100

.OPTIONS VNTOL= 1.0m

.PROBE V(*) I(*) W(*) D(*) NOISE(*)

.INC ".\test3-SCHEMATIC1.net"

**** INCLUDING test3-SCHEMATIC1.net ****

* source TEST3

X_M1A N00413 N00640 N00431 PHN210/PLP

R_R1 0 N00431 0.1

C_C1 N00563 N00685 0.1u

E_U1 N00685 0 VALUE {LIMIT(V(N00966,N00563)*1E6,0V,+12V)}

R_R2 N00685 N00640 10k

V_V3 N01122 0 3Vdc

R_R3 N00563 N00431 1k

R_R4 0 N00966 1k

V_V5 N00413 0 5Vdc

R_R5 N00966 N01122 9k

**** RESUMING test3-schematic1-test3.sim.cir ****

.END

**** 06/17/20 10:19:15 ********* PSpice 9.2 (Mar 2000) ******** ID# 1 ********

** Profile: "SCHEMATIC1-test3" [ E:\1-3 ACimpedance\CircuitDesignSim\mycapturet3\test3-schematic1-test3.sim ]

**** Diode MODEL PARAMETERS

******************************************************************************

X_M1A.Dbody

IS 258.000000E-15

N 1.002

IKF 10.49

BV 30

IBV 10.000000E-06

RS .1773

TT 80.000000E-09

CJO 623.500000E-12

VJ .7055

M .4718

**** 06/17/20 10:19:15 ********* PSpice 9.2 (Mar 2000) ******** ID# 1 ********

** Profile: "SCHEMATIC1-test3" [ E:\1-3 ACimpedance\CircuitDesignSim\mycapturet3\test3-schematic1-test3.sim ]

**** MOSFET MODEL PARAMETERS

******************************************************************************

X_M1A.MOST1 X_M1A.MOST2

NMOS NMOS

LEVEL 3 1

L 2.000000E-06 2.000000E-06

W .54 .54

VTO 2.2 -3.9

KP 20.580000E-06 20.580000E-06

GAMMA 0 0

PHI .6 .6

LAMBDA 0 0

RD .056

RS .02 .02

IS 10.000000E-15 10.000000E-15

JS 0 0

PB .8 .8

PBSW .8 .8

CJ 0 0

CJSW 0 0

CGSO 0 0

CGDO 0 0

CGBO 0 0

TOX 100.000000E-09 0

XJ 0 0

UCRIT 10.000000E+03 10.000000E+03

DIOMOD 1 1

VFB 0 0

LETA 0 0

WETA 0 0

U0 0 0

TEMP 0 0

VDD 0 0

XPART 0 0

ERROR -- Convergence problem in transient bias point calculation

Last node voltages tried were:

NODE VOLTAGE NODE VOLTAGE NODE VOLTAGE NODE VOLTAGE

(N00413) 1.1600 (N00431) .0696 (N00563) .0696 (N00640) 2.7840

(N00685) 2.7840 (N00966) .0696 (N01122) .6960 (X_M1A.4) 1.1600

These devices failed to converge:

E_U1

ERROR -- Discontinuing simulation due to convergence problem

===============================================

Attachments

Last edited by a moderator: