Junus2012

Advanced Member level 5

Hello friends,

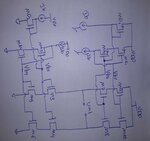

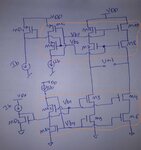

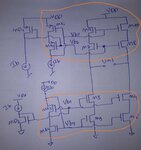

below is an example of folded cascode ampliifer,

you see transistors M2-to-M10, these transistors are biased with VB1-to-VB4.

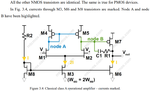

While VB1 and VB2 is a biasing voltage for the cascode transistors M3,M4,M7 and M8 and it is not critical, but Vb3 and VB4 are biasing the upper and down mirror, if the transistors generating these voltages are not matched to the transistor in the ampliifer this will lead to mismatching in the current.

My question, when you design such circuit, do you consider to match the biasing circuit to the core circuit,

I have searched in many literature and I usually see them seperating both, I am not sure how they are matching it

Thank you very much

Best Regards

below is an example of folded cascode ampliifer,

you see transistors M2-to-M10, these transistors are biased with VB1-to-VB4.

While VB1 and VB2 is a biasing voltage for the cascode transistors M3,M4,M7 and M8 and it is not critical, but Vb3 and VB4 are biasing the upper and down mirror, if the transistors generating these voltages are not matched to the transistor in the ampliifer this will lead to mismatching in the current.

My question, when you design such circuit, do you consider to match the biasing circuit to the core circuit,

I have searched in many literature and I usually see them seperating both, I am not sure how they are matching it

Thank you very much

Best Regards