carporsche

Junior Member level 2

Hi All

I wanted to know if anyone can give me an insight to this particular problem i have.

Basically, i have a current conveyor (single ended) and need a deterministic DC level at the output. How would i go about setting the dc- level.

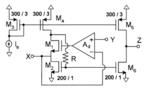

Attached is a figure. I would like to set the DC-level @ node Z

source : Carvajal, Ramón González, et al. "The flipped voltage follower: A useful cell for low-voltage low-power circuit design." Circuits and Systems I: Regular Papers, IEEE Transactions on 52.7 (2005): 1276-1291.

I wanted to know if anyone can give me an insight to this particular problem i have.

Basically, i have a current conveyor (single ended) and need a deterministic DC level at the output. How would i go about setting the dc- level.

Attached is a figure. I would like to set the DC-level @ node Z

source : Carvajal, Ramón González, et al. "The flipped voltage follower: A useful cell for low-voltage low-power circuit design." Circuits and Systems I: Regular Papers, IEEE Transactions on 52.7 (2005): 1276-1291.