Follow along with the video below to see how to install our site as a web app on your home screen.

Note: This feature may not be available in some browsers.

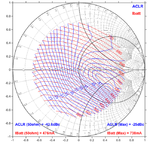

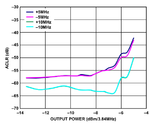

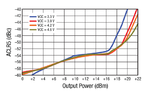

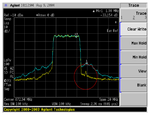

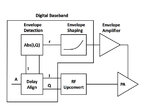

ACLR (Adjacent Channel Leakage Ratio) is a very important specification in WCDMA systems for the transmitter, especially the power amplifier. It is defined as the ratio of the power in the adjacent channel to the power in the user (wanted) channel,

ACLR = 10 log (PADJACENT/PWANTED) [dBc]

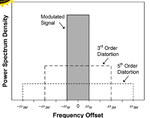

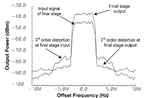

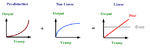

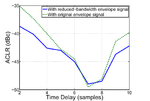

effect occurs with broadband signals and is by the odd terms (IM3, IM5, etc) of the transfer function of building block.

The first adjacent channel distortion (ACLR1-adjacent) result from both the 3rd order and the 5th order distortion mechanisms, whereas the second adjacent channel (ACLR2-alternate) is dominated by the 5th order distortion mechanisms. The overall distortion at IM3 frequency (ACLR1) is a vector sum of the distortions generated by the third and fifth order nonlinearity.

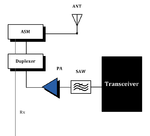

The linearity of the transmitter chain is the main contributor keeping good ACLR.