pic.programmer

Advanced Member level 3

In this page

https://www.mikroe.com/chapters/view/52/chapter-4-timers/#ch4.4.2

section 4.4.2 it says one has to use T1CK pin. Should I use T1CK or T2CK pin ?

Please explain more about Time base.

I think you gave info related to 32 bit Timer. I need for 32 bit counter.

Edit:

Why in this page

https://www.mikroe.com/chapters/view/52/chapter-4-timers/#ch4.4.2

section 4.4.2

T3CON is not configured ?

If I want the Timer2&3 counter to overflow at 4,29,49,67,296 should I load PR2 and PR3 with 0xFFFFFFFF ?

Is this code correct ?

I think

also works. Right ?

https://www.mikroe.com/chapters/view/52/chapter-4-timers/#ch4.4.2

section 4.4.2 it says one has to use T1CK pin. Should I use T1CK or T2CK pin ?

Please explain more about Time base.

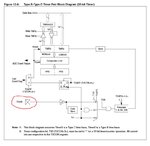

A 32-bit timer module can be formed by combining a Type B and a Type C 16-bit timer module.

The Type C time base becomes the MSWord of the combined timer and the Type B time base is

the LSWord.

When configured for 32-bit operation, the control bits for the Type B time base control the operation

of the 32-bit timer. The control bits in the TxCON register for the Type C time base have no effect.

For interrupt control, the combined 32-bit timer uses the interrupt enable, interrupt flag and

interrupt priority control bits of the Type C time base. The interrupt control and status bits for the

Type B time base are not used during 32-bit timer operation.

The following configuration settings assume Timer3 is a Type C time base and Timer2 is a Type B

time base:

I think you gave info related to 32 bit Timer. I need for 32 bit counter.

Edit:

Why in this page

https://www.mikroe.com/chapters/view/52/chapter-4-timers/#ch4.4.2

section 4.4.2

T3CON is not configured ?

If I want the Timer2&3 counter to overflow at 4,29,49,67,296 should I load PR2 and PR3 with 0xFFFFFFFF ?

Is this code correct ?

Code:

void Timer23Int() org 0x22{ //Address in the interrupt vector table of timer3

IFS0 = 0; // Clear interrupt request

}

void main(){

TRISC = 0xFFFF; //PORTC<13>=1 T2CK is input pin

T3IF_bit = 1;

PR2 = 0xFFFF; //Interrupt peiod is 10 clocks

PR3 = 0xFFFF; //Total PR3/2=0*65536 + 10

T2CON = 0x800A; //Timer2/3 is synchronous counter of external pulses

while(1);

}I think

Code:

T2CON = 0x8002;also works. Right ?

Last edited: