elec-eng

Full Member level 5

Strange problem in HFSS port sizing, and result comparison to ADS and Sonnet

Hi,

I am facing a problem with HFSS port sizing. I am simulating a simple microstrip line of width microstrip_w=50um on top of a substrate of thickness 0.3um, with perfect_E boundary assigned to the bottom face of the radiation box to act as a ground plane. The microstrip has zero thickness. the structure is shown:

I use a waveguide port with height=9*substrate_h, de-embedding, normalization impedance of 50ohm, one mode, no integration line "so Zpi used for Z0".

I am interested in the imaginary part of this line "An open microstrip is capacitive", as I will use it later to match the inductive impedance of slot antenna.

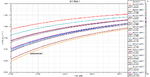

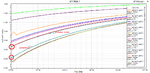

However, results change dramatically with just small change in port size. To illustrate to you more, I have made a variable port width: port_w=prefactor*microstrip_w , where prefactor changes from 8 to 16. I get near-correct results for only prefactor =13, 14, and 15 "those curves are encircled by the red circle" in the next figure:

For all those curves, convergence is reached.

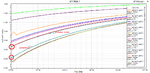

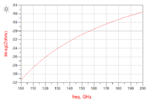

I know that those circled results are correct because I simulated the same structure using both ADS and Sonnet, and the result is nearly the same as shown below:

ADS:

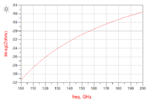

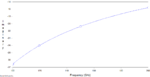

Sonnet:

I even simulated "port only" with 5 modes and made sure than no higher order modes propagate.

Please tell me how to overcome this problem. The results are very sensitive to small changes in port size, "even 12.5 prefactor is very different than 12 and different than 13, and no constant trend in the resulting curves"

Why this happens and how to size the port in this case to get correct results without having to simulate using other softwares.

I need to get reliable results urgently as I will use it for a bigger problem for my degree project, and unfortunately I am running out of time

Thanks in advance

Hi,

I am facing a problem with HFSS port sizing. I am simulating a simple microstrip line of width microstrip_w=50um on top of a substrate of thickness 0.3um, with perfect_E boundary assigned to the bottom face of the radiation box to act as a ground plane. The microstrip has zero thickness. the structure is shown:

I use a waveguide port with height=9*substrate_h, de-embedding, normalization impedance of 50ohm, one mode, no integration line "so Zpi used for Z0".

I am interested in the imaginary part of this line "An open microstrip is capacitive", as I will use it later to match the inductive impedance of slot antenna.

However, results change dramatically with just small change in port size. To illustrate to you more, I have made a variable port width: port_w=prefactor*microstrip_w , where prefactor changes from 8 to 16. I get near-correct results for only prefactor =13, 14, and 15 "those curves are encircled by the red circle" in the next figure:

For all those curves, convergence is reached.

I know that those circled results are correct because I simulated the same structure using both ADS and Sonnet, and the result is nearly the same as shown below:

ADS:

Sonnet:

I even simulated "port only" with 5 modes and made sure than no higher order modes propagate.

Please tell me how to overcome this problem. The results are very sensitive to small changes in port size, "even 12.5 prefactor is very different than 12 and different than 13, and no constant trend in the resulting curves"

Why this happens and how to size the port in this case to get correct results without having to simulate using other softwares.

I need to get reliable results urgently as I will use it for a bigger problem for my degree project, and unfortunately I am running out of time

Thanks in advance

Last edited: