forkconfig

Member level 1

I'm working on a hobby project and I have run into a problem with arbitration.

Is there any online lectures/course notes or books you can suggest to help me?

Also if you don't mind helping me here is my problem.

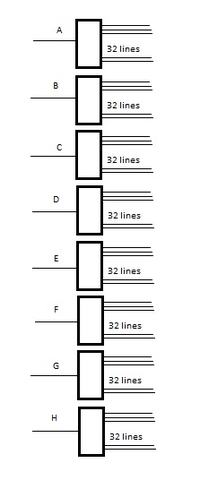

I have 256 clients, clients can make requests at any time.

At first what I did is I had a shared bus where clients could make requests on. But how would I ensure multiple clients don't request at the same time?

So then I added dedicated request lines. But then the issue was, now I have to check ALL 256 lines in the one clock cycle, so if in the next clock cycle, people want to make a request I don't loose those, and I maintain first come first serve sequence.

I'd really appreciate any help.

Thanks

Oh I'm using Verilog by the way.

Is there any online lectures/course notes or books you can suggest to help me?

Also if you don't mind helping me here is my problem.

I have 256 clients, clients can make requests at any time.

At first what I did is I had a shared bus where clients could make requests on. But how would I ensure multiple clients don't request at the same time?

So then I added dedicated request lines. But then the issue was, now I have to check ALL 256 lines in the one clock cycle, so if in the next clock cycle, people want to make a request I don't loose those, and I maintain first come first serve sequence.

I'd really appreciate any help.

Thanks

Oh I'm using Verilog by the way.