Decreasing sizes of semiconductor process geometries and greater number of metal layers, interconnections and components result in a large number of parasitic devices during netlist extraction. This can be problematic for simulation and verification engineers.

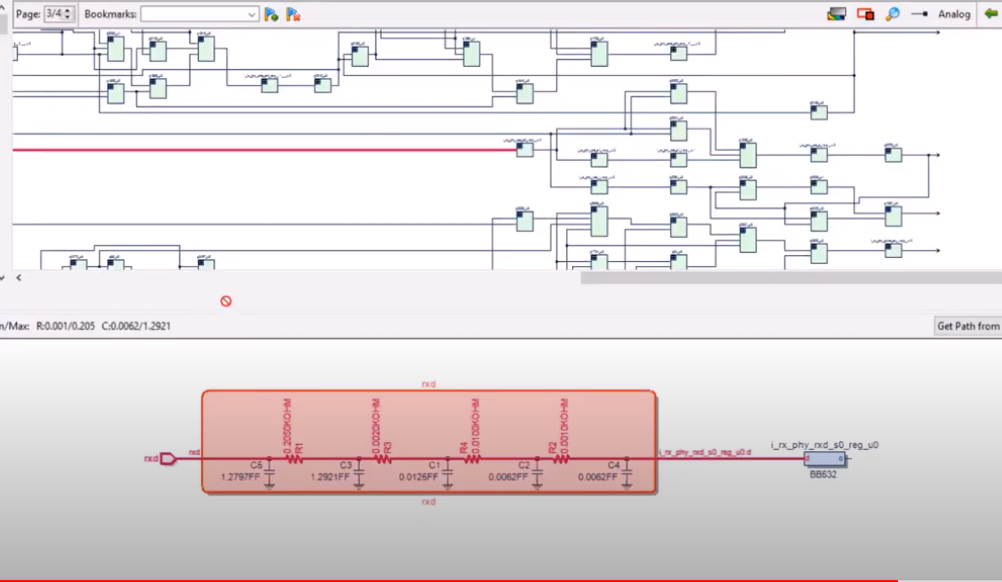

Fortunately, SPEF (standard parasitic exchange format) and DSPF (Detailed Standard Parasitic Format) interfaces can now be used through certain visualization tools to easily analyze and explore parasitic structures and to comprehend and optimize timing, signal integrity or IR-drop within their designs. SPEF file format is an IEEE standard to define parasitic networks, with precise information about interconnections and the related parasitic components.

See this video to learn how a certain SPEF interface can give design engineers specific details about the post-layout interconnections on their chips, for easier visualization and navigation of parasitic netlists and to pinpoint post-layout problems. Pruning and creating post-layout SPICE netlists of critical circuit fragments is also possible. These netlist fragments can then be used for fast circuit simulation to accelerate post layout simulation.

Fortunately, SPEF (standard parasitic exchange format) and DSPF (Detailed Standard Parasitic Format) interfaces can now be used through certain visualization tools to easily analyze and explore parasitic structures and to comprehend and optimize timing, signal integrity or IR-drop within their designs. SPEF file format is an IEEE standard to define parasitic networks, with precise information about interconnections and the related parasitic components.

See this video to learn how a certain SPEF interface can give design engineers specific details about the post-layout interconnections on their chips, for easier visualization and navigation of parasitic netlists and to pinpoint post-layout problems. Pruning and creating post-layout SPICE netlists of critical circuit fragments is also possible. These netlist fragments can then be used for fast circuit simulation to accelerate post layout simulation.