hdrohithd

Newbie

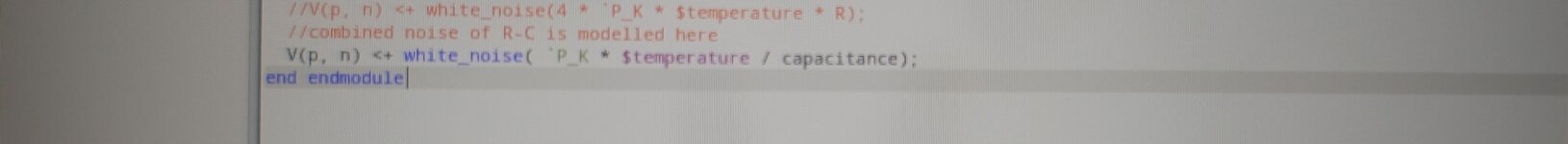

I have a question regarding modelling of kt/c noise. I tried modelling it using verilog-a .

I have KT/C spectral noise as 207.14pV^2/Hz (theoretical as well as in noise analysis)

Here I am measuring noise generated at the source in virtuoso noise analysis and it's coming as expected.

--- attachment: 1.jpg, 2.jpg

But when I do the transient analysis with input voltage for the resistor = 0-0.9v sine wave, ideally I am thinking sine wave + noise Voltage have to be :

√spectral noise power = √207.14pV^2/Hz = 14.39uV

Input voltage is 0.9v sine wave. So the sine wave with noise have to be random noise with average magnitude of 14.39uV with superimposed on vsin.

But I am getting very large transient voltage at the input. Noise Voltage is around 4 volts.

--- attachment:

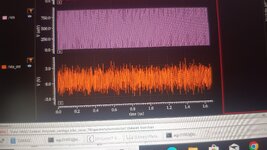

3.jpg showing vin -> pure sine wave, and vin_err -> showing sine wave with noise.

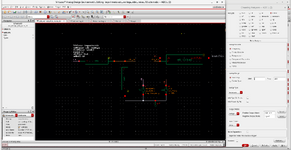

4.jpg showing circuit and transient noise option setting in the simulator.

Mainly I want to add this transient noise and want to measure how noise affects ADC performance matrix like snr, enob etc..

I have KT/C spectral noise as 207.14pV^2/Hz (theoretical as well as in noise analysis)

Here I am measuring noise generated at the source in virtuoso noise analysis and it's coming as expected.

--- attachment: 1.jpg, 2.jpg

But when I do the transient analysis with input voltage for the resistor = 0-0.9v sine wave, ideally I am thinking sine wave + noise Voltage have to be :

√spectral noise power = √207.14pV^2/Hz = 14.39uV

Input voltage is 0.9v sine wave. So the sine wave with noise have to be random noise with average magnitude of 14.39uV with superimposed on vsin.

But I am getting very large transient voltage at the input. Noise Voltage is around 4 volts.

--- attachment:

3.jpg showing vin -> pure sine wave, and vin_err -> showing sine wave with noise.

4.jpg showing circuit and transient noise option setting in the simulator.

Mainly I want to add this transient noise and want to measure how noise affects ADC performance matrix like snr, enob etc..