pnsakanjankumar

Member level 2

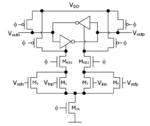

I am designing a dynamic comparator as shown in figure. This circuit works as follows.

When phi is 0, the voutn and voutp are held at vdd and when phi is 1, one of the side is pulled down and finally the cross coupled inverters settle to a stable state.

Now I want to find static and dynamic resolution. I found the static resolution by changing the input DC voltages and by observing the output response.

How to find dynamic resolution and what does it actually mean?

When phi is 0, the voutn and voutp are held at vdd and when phi is 1, one of the side is pulled down and finally the cross coupled inverters settle to a stable state.

Now I want to find static and dynamic resolution. I found the static resolution by changing the input DC voltages and by observing the output response.

How to find dynamic resolution and what does it actually mean?