FreshmanNewbie

Advanced Member level 1

Can someone tell me what does one mean, when it is stated, "Some IC has "weak" pierce oscillators"?

What is the actually meaning when it one says a "weak pierce oscillator"?

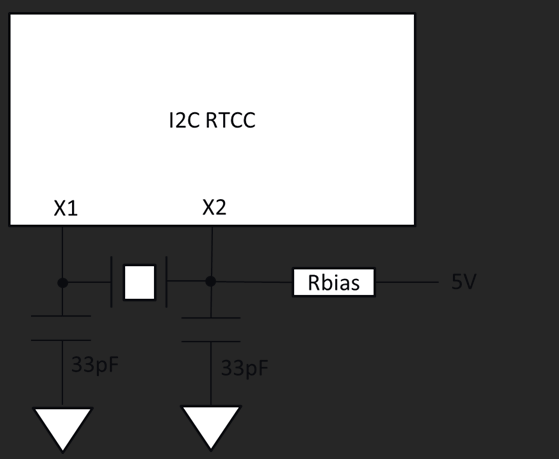

Also, why is this configuration preferred when the pierce oscillator is weak?

What does this bias current do ? Does it make the oscillator strong?

The Resistor value is 4.7Meg

What is the actually meaning when it one says a "weak pierce oscillator"?

Also, why is this configuration preferred when the pierce oscillator is weak?

What does this bias current do ? Does it make the oscillator strong?

The Resistor value is 4.7Meg