Paul98

Member level 5

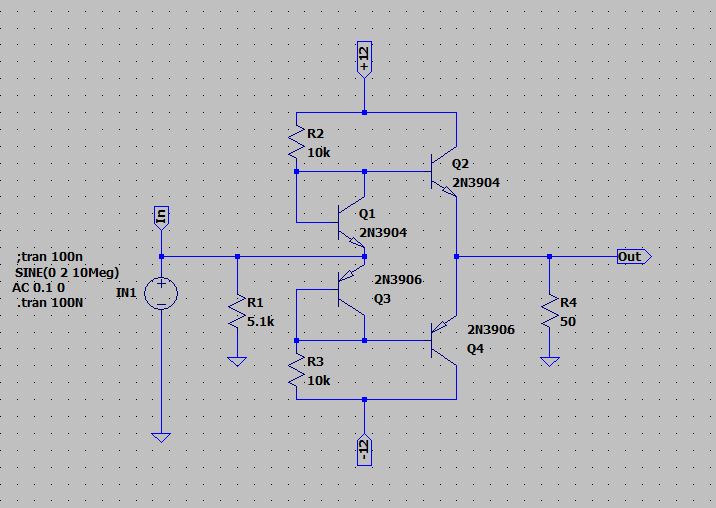

Hi ,i've drew this circuit.

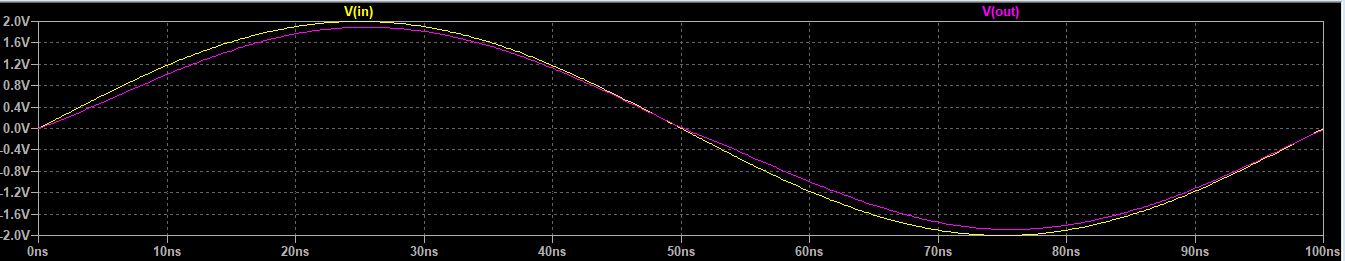

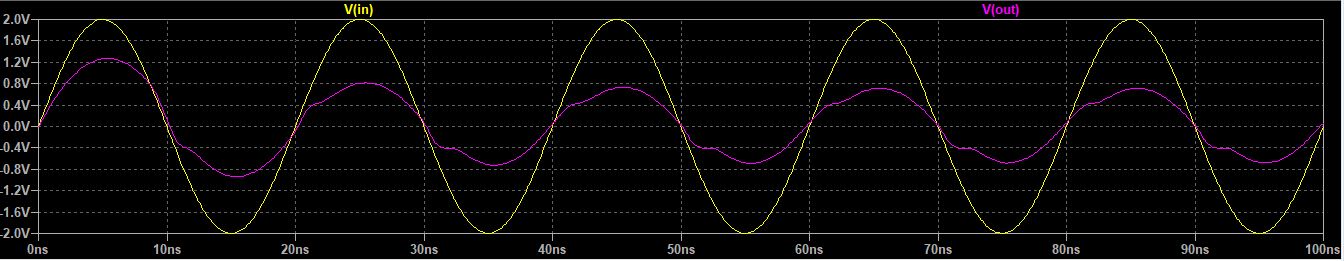

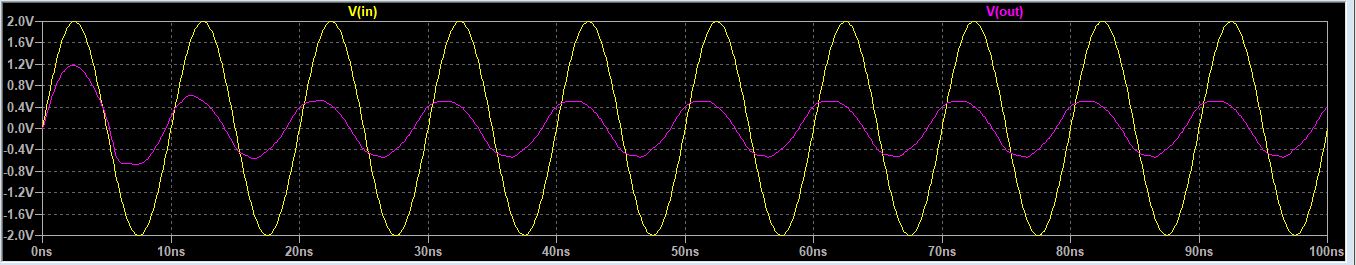

I have seen that the output wave is distorted as the value of the output load decreases, and obviously reducing the load also decreases the amplitude. Now this is a buffer where I would have expected better behavior under low loads but it didn't happen. Is there any way to limit this distortion and loss of amplitude? My first suspicion is that the transistor type are not suitable for low loads despite their Ft being covered. Thanks.

I have seen that the output wave is distorted as the value of the output load decreases, and obviously reducing the load also decreases the amplitude. Now this is a buffer where I would have expected better behavior under low loads but it didn't happen. Is there any way to limit this distortion and loss of amplitude? My first suspicion is that the transistor type are not suitable for low loads despite their Ft being covered. Thanks.