Boris.b

Newbie

Hey,

I am trying to instantiate two modules via top one. The modules are an SPI one, and one that should toggle LED when byte is received.

When i try to use only one of the modules it works just fine, but when i instantiate them to try and connect them the MOSI line is always unconnected.

here are the files.

spi_slave.sv

led_blink.sv

top_module.sv

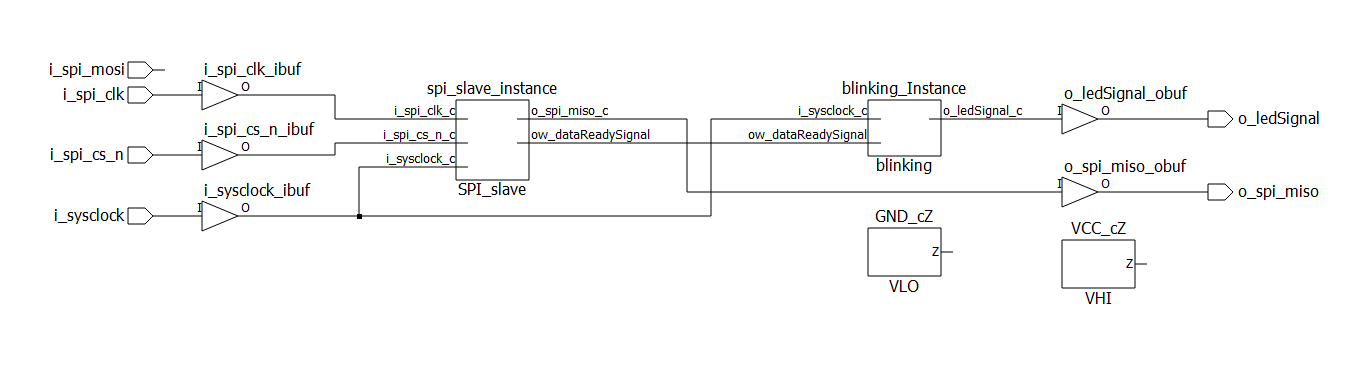

output from the netlist analyzer:

From what i read online this should work, but it does not. Any help will be greatly appriciated.

Best Regards

I am trying to instantiate two modules via top one. The modules are an SPI one, and one that should toggle LED when byte is received.

When i try to use only one of the modules it works just fine, but when i instantiate them to try and connect them the MOSI line is always unconnected.

here are the files.

spi_slave.sv

Code:

module SPI_slave(SysClk, SCK, MOSI, MISO, SSEL, LED, rx_buf, tx_buf, rx_valid );

input SysClk;

input reg SCK, SSEL, MOSI;

output MISO;

output LED;

input reg [7:0] tx_buf; // byte to transmit

output reg [7:0] rx_buf; // byte that is has been received

output reg rx_valid; // byte received flag

// sync clocks to avoid cross domain metastability

// sync SCK to the FPGA clock using a 3-bits shift register

reg [2:0] SCKr; always @(posedge SysClk) SCKr <= {SCKr[1:0], SCK};

wire SCK_risingedge = (SCKr[2:1]==2'b01); // now we can detect SCK rising edges

wire SCK_fallingedge = (SCKr[2:1]==2'b10); // and falling edges

// same thing for SSEL

reg [2:0] SSELr; always @(posedge SysClk) SSELr <= {SSELr[1:0], SSEL};

wire SSEL_active = ~SSELr[1]; // SSEL is active low

wire SSEL_startmessage = (SSELr[2:1]==2'b10); // message starts at falling edge

wire SSEL_endmessage = (SSELr[2:1]==2'b01); // message stops at rising edge

// and for MOSI

reg [1:0] MOSIr; always @(posedge SysClk) MOSIr <= {MOSIr[0], MOSI};

wire MOSI_Sync_Data = MOSIr[1]; // synchronous version of MOSI input

// we handle SPI in 8-bits format, so we need a 3 bits counter to count the bits as they come in

reg [2:0] bitcnt;

reg [7:0] byte_data_received;

always @(posedge SysClk)

begin

if(~SSEL_active)

bitcnt <= 3'b000;

else

if(SCK_risingedge)

begin

bitcnt <= bitcnt + 3'b001;

// implement a shift-left register (since we receive the data MSB first)

rx_buf <= {rx_buf[6:0], MOSI_Sync_Data};

end

end

always @(posedge SysClk) rx_valid <= SSEL_active && SCK_risingedge && (bitcnt==3'b111);

// we use the LSB of the data received to control an LED

reg LED;

always @(posedge SysClk) if(rx_valid) LED <= ~LED;

reg [7:0] byte_data_sent;

reg [7:0] cnt; // keep count of the received messages

always @(posedge SysClk) if(SSEL_startmessage) cnt<=cnt+8'h1; // count the messages

always @(posedge SysClk)

if(SSEL_active)

begin

if(SSEL_startmessage)

byte_data_sent <= cnt; // load count into transfer buffer

else

if(SCK_fallingedge)

begin

if(bitcnt==3'b000)

byte_data_sent <= cnt; // after that, we send count value

else

byte_data_sent <= {byte_data_sent[6:0], 1'b0}; // shift register

end

end

assign MISO = byte_data_sent[7]; // send MSB first

// we assume that there is only one slave on the SPI bus

// so we don't bother with a tri-state buffer for MISO

// otherwise we would need to tri-state MISO when SSEL is inactive

endmoduleled_blink.sv

Code:

// Slow blinking a LED

/* module */

module blinking (

input DataReceivedFlag,

input clk,

output reg LedOutput

);

always @(posedge clk) begin

if(DataReceivedFlag) begin

LedOutput <= ~LedOutput;

end

end

endmoduletop_module.sv

Code:

module top_spi (

// genral signals

input i_sysclock,

output o_ledSignal,

// spi signals

input reg i_spi_clk, i_spi_cs_n, i_spi_mosi,

output reg o_spi_miso

);

wire ow_dataReadySignal;

wire mosi_signal;

blinking blinking_Instance(.DataReceivedFlag(ow_dataReadySignal), .clk(i_sysclock), .LedOutput(o_ledSignal));

SPI_slave spi_slave_instance(

.SysClk(i_sysclock),

.SCK(i_spi_clk),

.SSEL(i_spi_cs_n),

.MOSI(i_spi_mosi),

.MISO(o_spi_miso),

.rx_valid(ow_dataReadySignal)

);

endmoduleoutput from the netlist analyzer:

From what i read online this should work, but it does not. Any help will be greatly appriciated.

Best Regards

Last edited: