GreatField

Newbie level 6

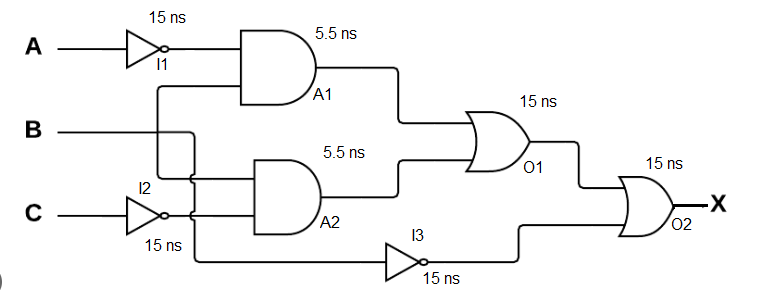

Suppose the circuit below, where each logic gate has a propagation delay given by (tPLH + tPHL) / 2.

The correct method of calculating the circuit's propagation delay would be to add the gates that take the longest time to reach the output, which in this case would be:

I1 + A1 + O1 + O2 = 50.5 ns ?

The correct method of calculating the circuit's propagation delay would be to add the gates that take the longest time to reach the output, which in this case would be:

I1 + A1 + O1 + O2 = 50.5 ns ?