knicklicht

Junior Member level 1

Hello all,

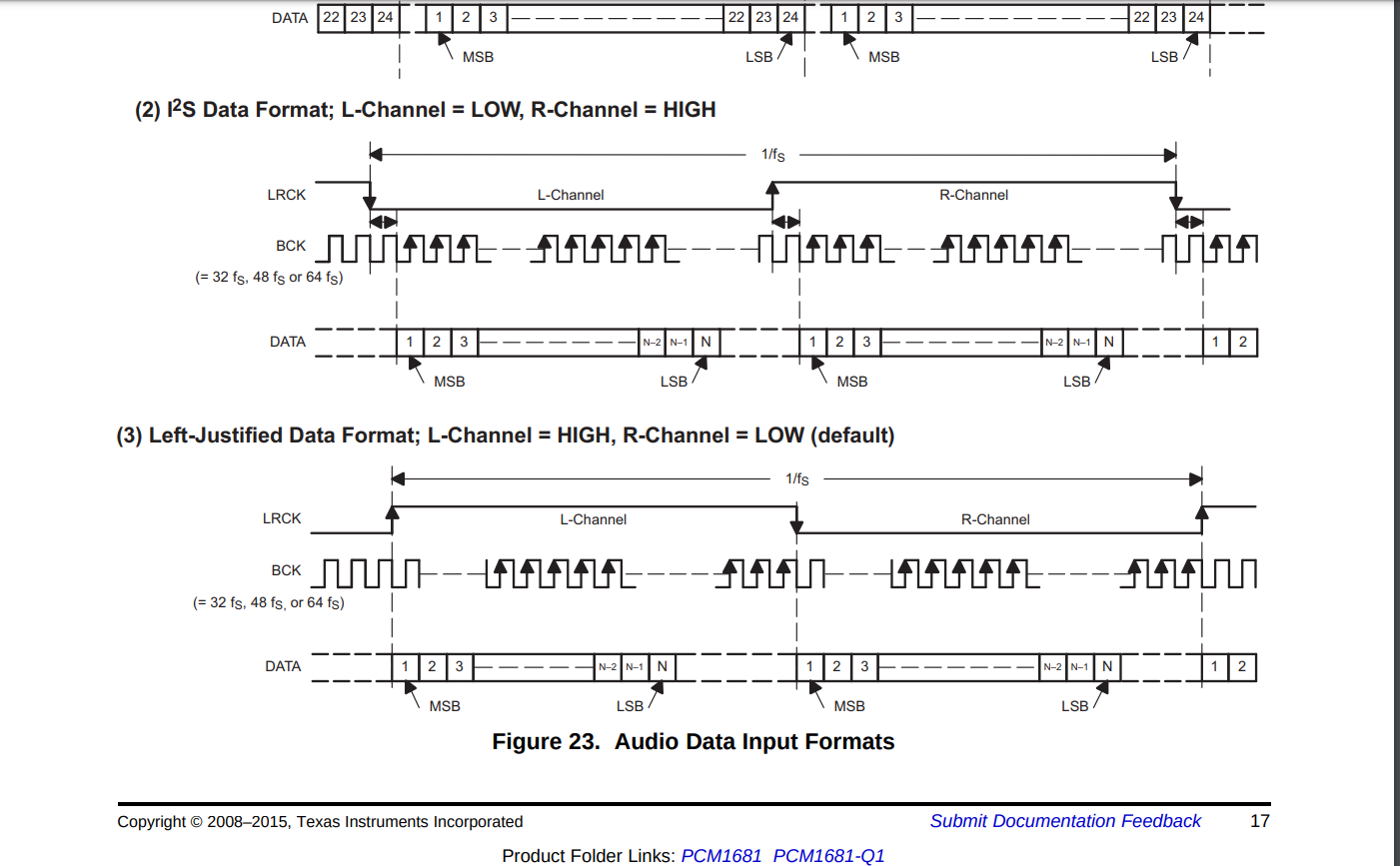

I am trying to generate a correct I2S signal to interact with my PCM1681 DAC using my FPGA. By default it uses a left justified signal but I want to use the "standard" I2S format. The datasheet states the following:

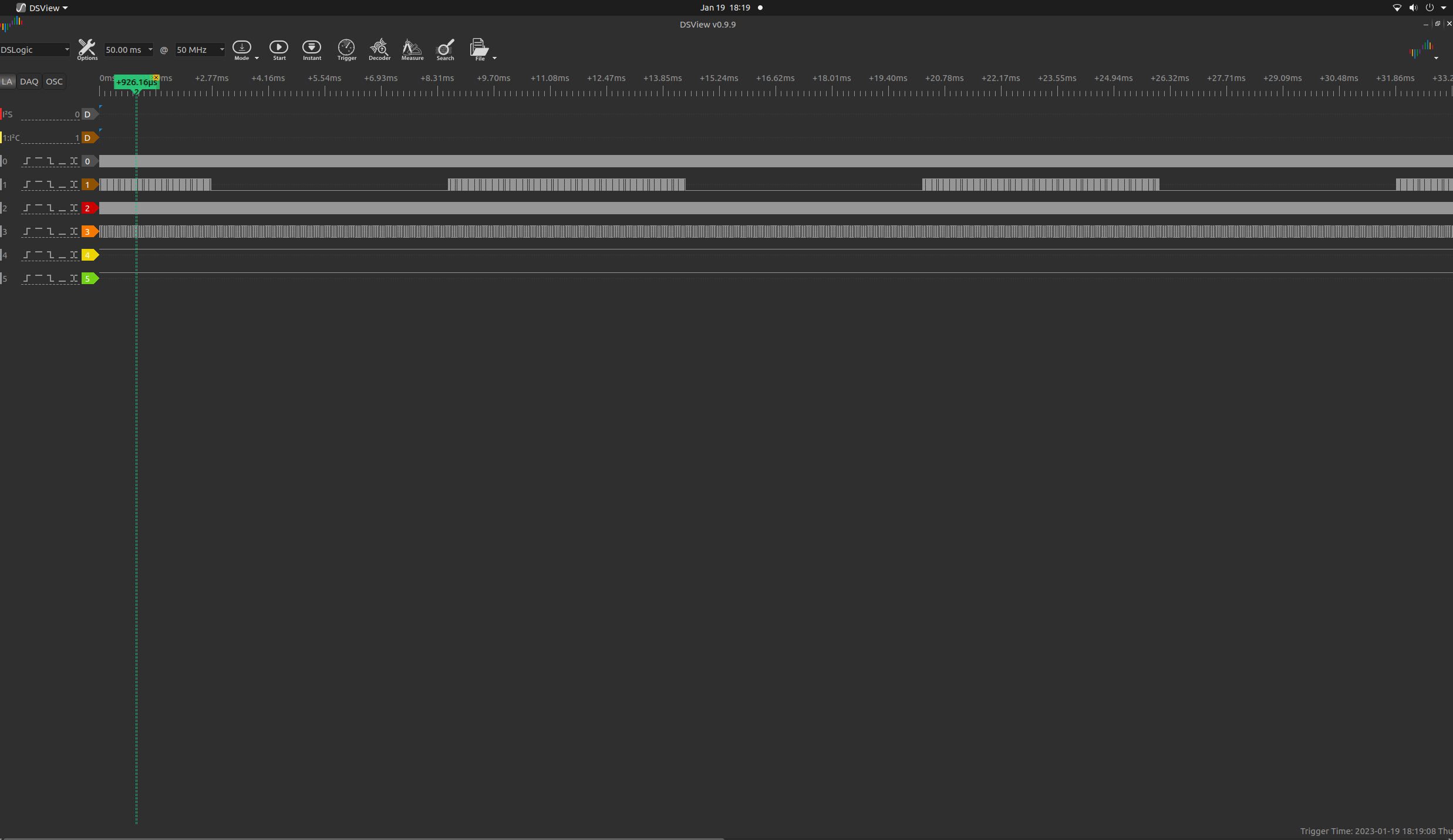

Next you can see my current signal. The data line alternates between 0x000000 and 0xffffff every 256 left right cycles.

Overall:

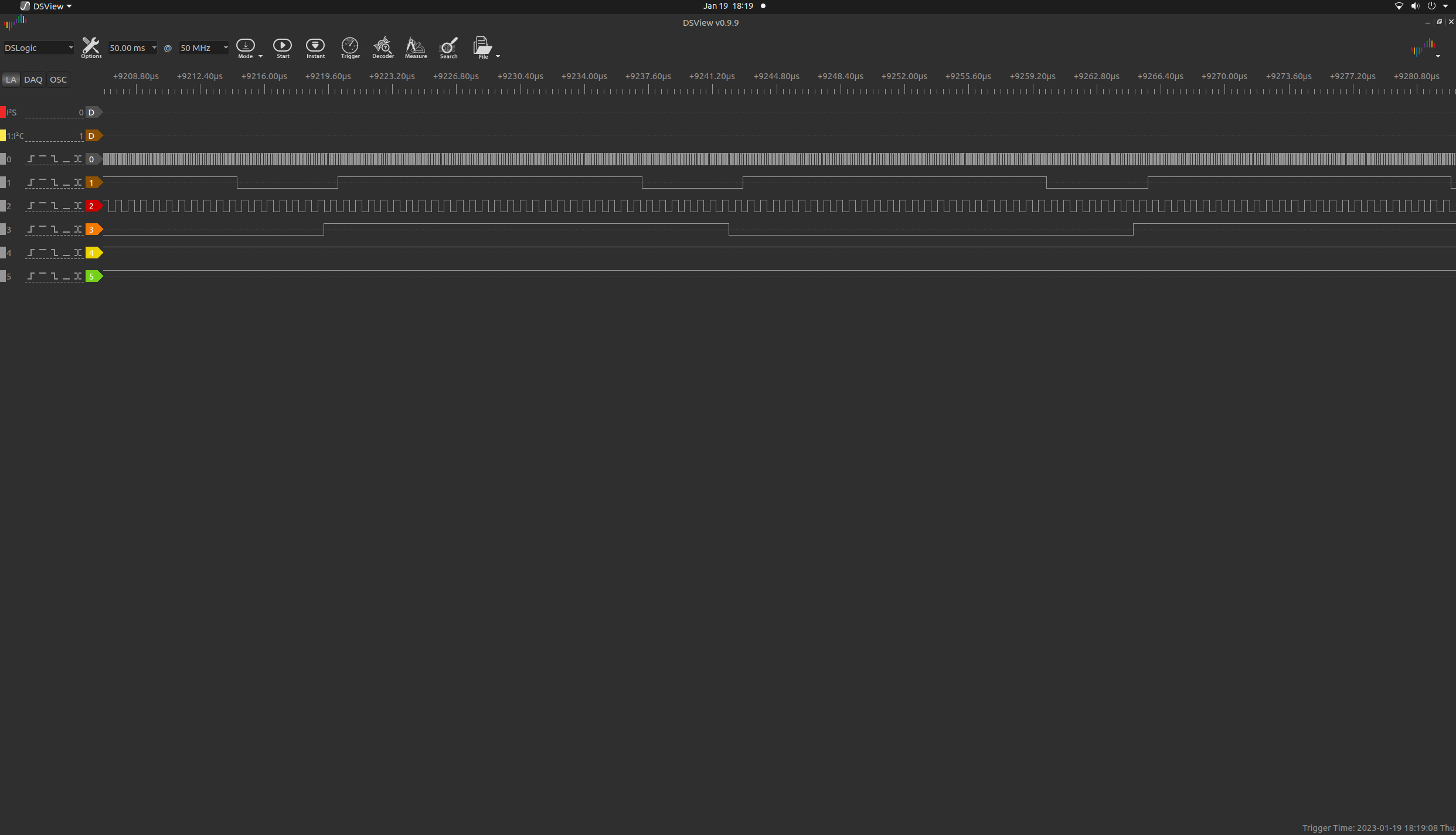

Closeup:

If I set the device to use left justified I see an analog square wave that alternates between 2.5V and 5V. This is because the first bit is set to 0 as per the standard I2S definition and I2S uses two's complement:

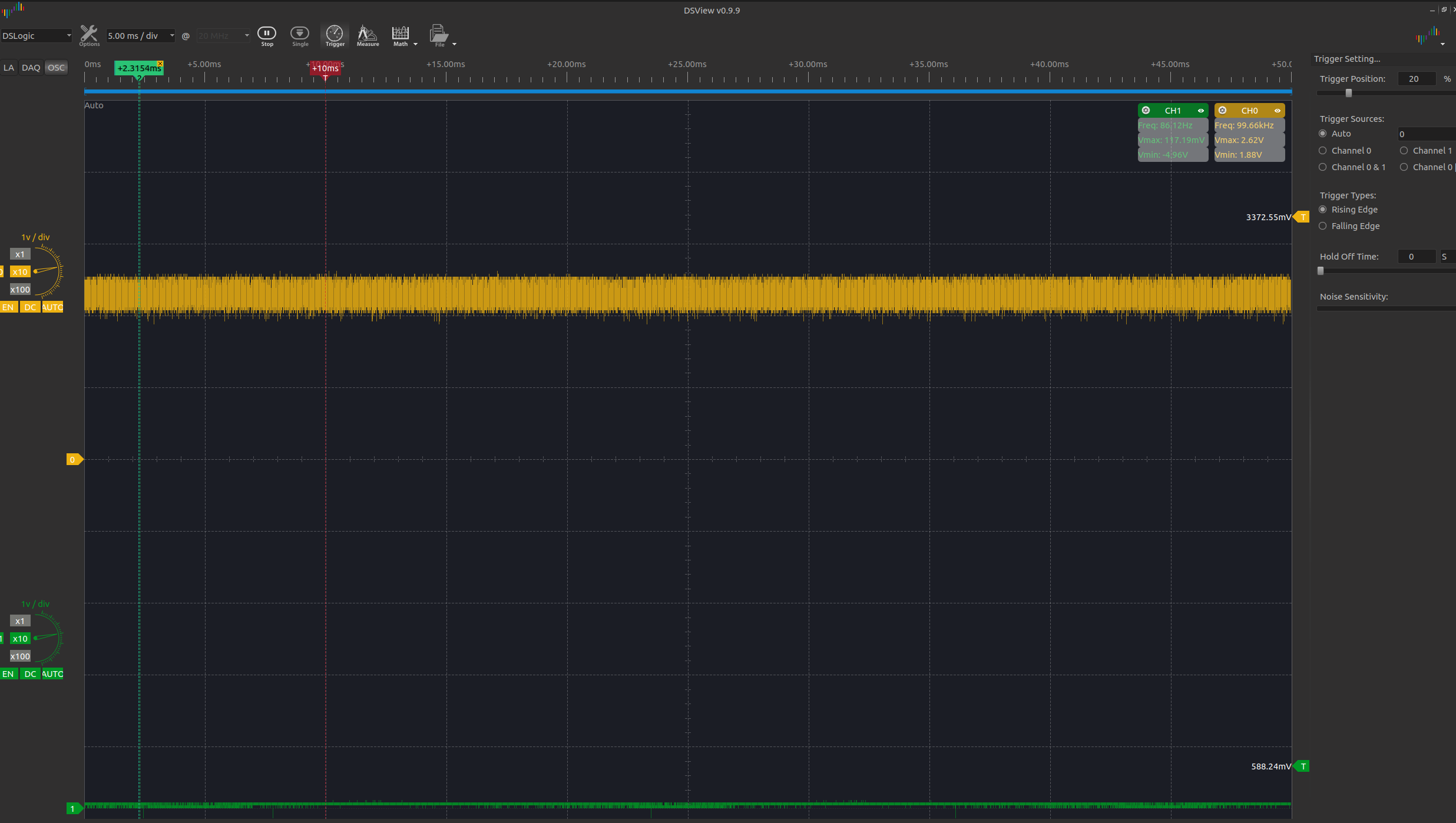

However, when I set the device to use standard I2S I should see a signal alternating between 0V and 2.5V (omitting the offset). However, this is not the case:

I have checked the signal again and again but I cannot find my mistake. I have also checked that I set the right value using I2C in register 0x09. Does someone see the issue?

I am trying to generate a correct I2S signal to interact with my PCM1681 DAC using my FPGA. By default it uses a left justified signal but I want to use the "standard" I2S format. The datasheet states the following:

Next you can see my current signal. The data line alternates between 0x000000 and 0xffffff every 256 left right cycles.

Overall:

Closeup:

If I set the device to use left justified I see an analog square wave that alternates between 2.5V and 5V. This is because the first bit is set to 0 as per the standard I2S definition and I2S uses two's complement:

However, when I set the device to use standard I2S I should see a signal alternating between 0V and 2.5V (omitting the offset). However, this is not the case:

I have checked the signal again and again but I cannot find my mistake. I have also checked that I set the right value using I2C in register 0x09. Does someone see the issue?