gahelton

Newbie level 4

This question relates to sending signals between two processes, and timing concerns.

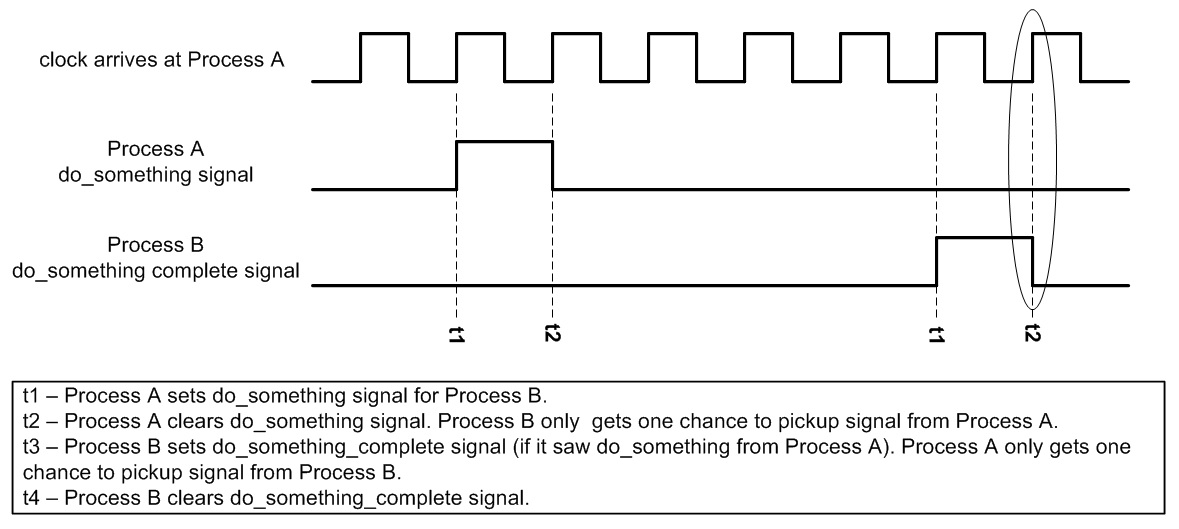

I have a system where Process A sends a signal to Process B. The signal is one clock cycle long beginning on the positive edge. Process B needs to capture this signal, do the requested logic, then signal a complete signal back to Process A, one cycle long, beginning on the positive edge of Process B clock. Ideally, Process A clock and Process B clock are the same clock (not withstanding any clock skew due to routing. (See attached picture).

My question is this. What are the pitfalls of such a design ? Can I guarantee that Process B, and Process A will see the signals from each other with a system like this ? It seems as if there were clock or data skew between processes that the signal may be missed. Would it be better to have Process B looking for the do_something signal on the falling edge of the clock . Likewise, sending the do_something_complete signal on the falling edge ? This out of phase clock relationship would take away the uncertainty of where the data is latched - wouldn't it ?

Of course, simulation works just fine like this, but will it always work once synthesised and loaded ?

Thanks.

I have a system where Process A sends a signal to Process B. The signal is one clock cycle long beginning on the positive edge. Process B needs to capture this signal, do the requested logic, then signal a complete signal back to Process A, one cycle long, beginning on the positive edge of Process B clock. Ideally, Process A clock and Process B clock are the same clock (not withstanding any clock skew due to routing. (See attached picture).

My question is this. What are the pitfalls of such a design ? Can I guarantee that Process B, and Process A will see the signals from each other with a system like this ? It seems as if there were clock or data skew between processes that the signal may be missed. Would it be better to have Process B looking for the do_something signal on the falling edge of the clock . Likewise, sending the do_something_complete signal on the falling edge ? This out of phase clock relationship would take away the uncertainty of where the data is latched - wouldn't it ?

Of course, simulation works just fine like this, but will it always work once synthesised and loaded ?

Thanks.