abuhafss

Full Member level 2

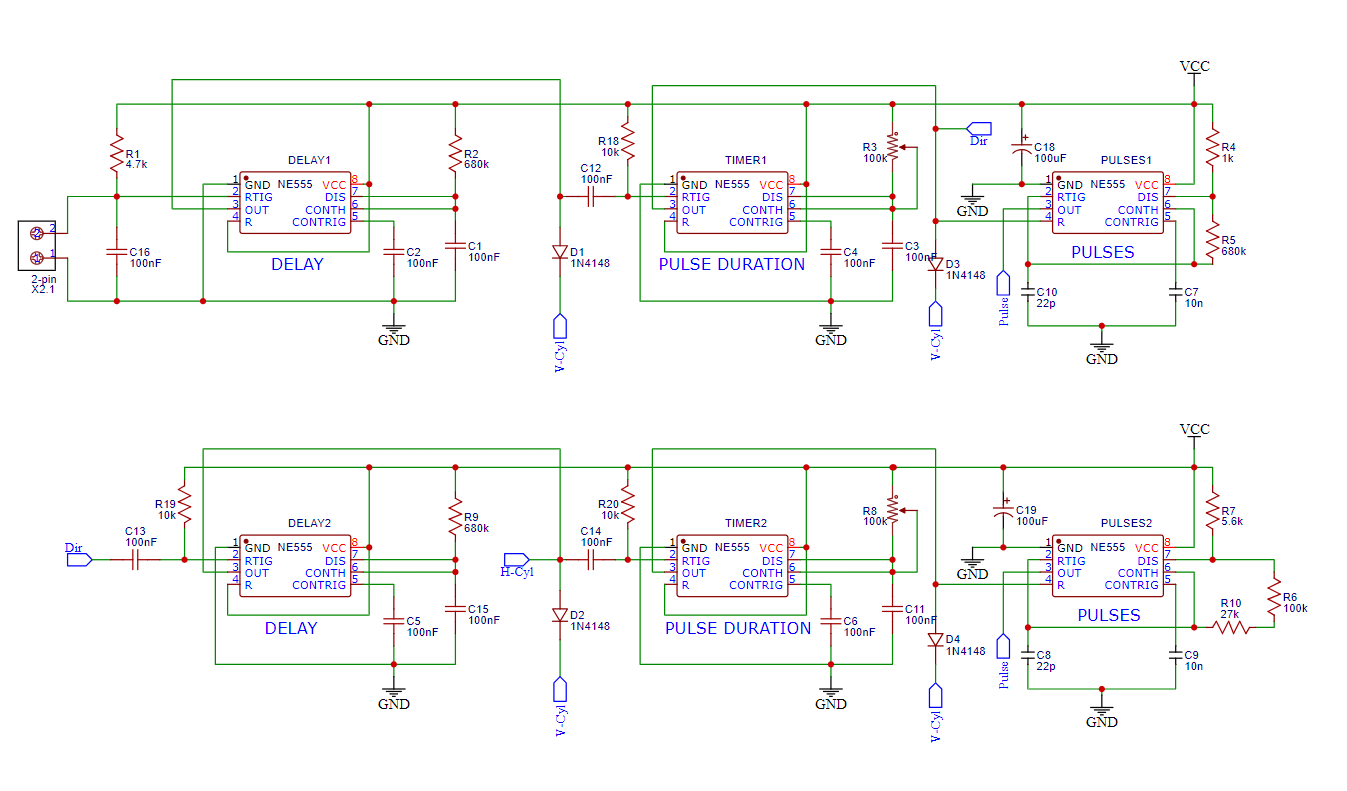

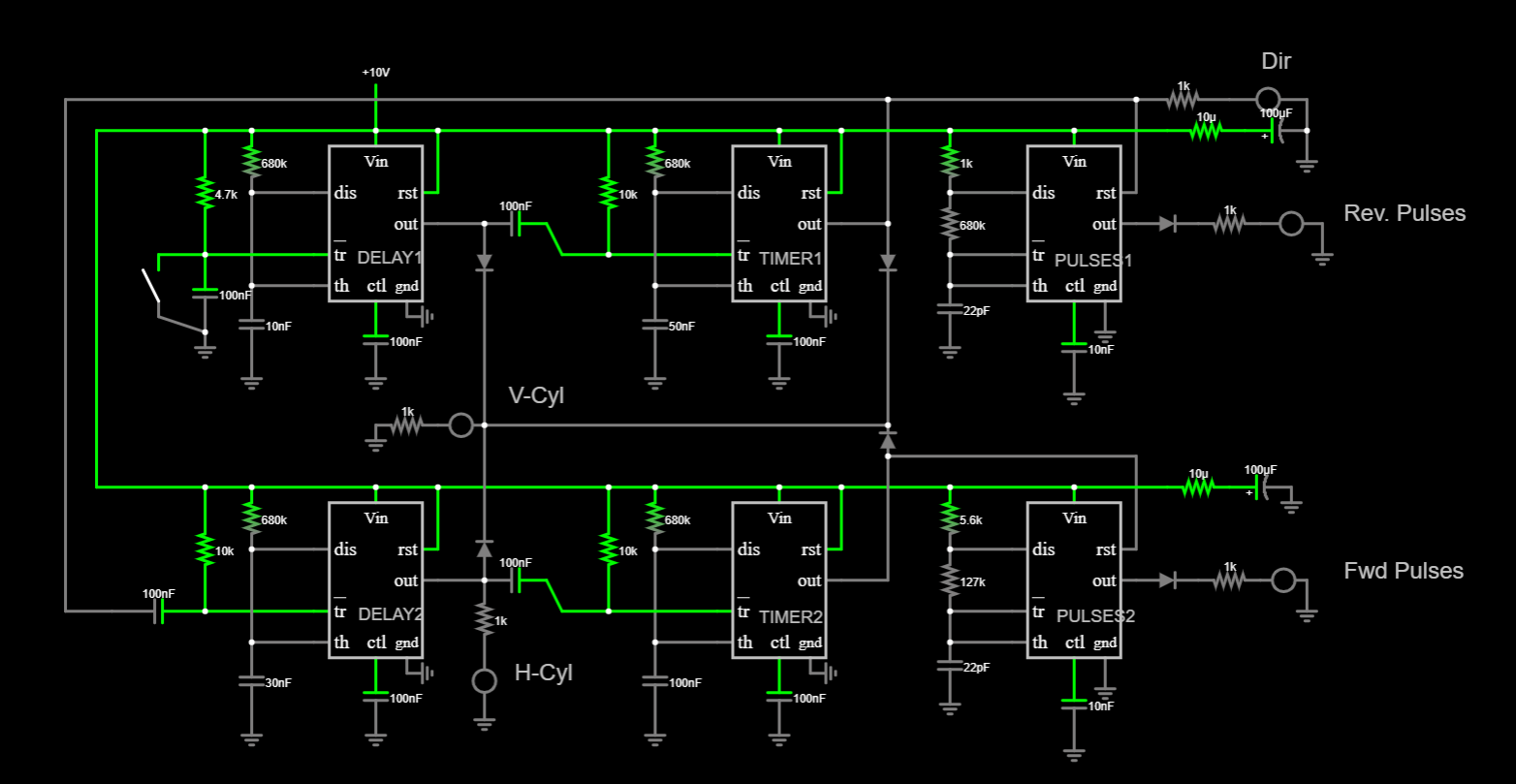

Here is a schematic containing a few cascaded 555 chips.

The flow of the circuit is as follows:

The flow of the circuit is as follows:

a) When a push button across C16 is pressed, DELAY1 (555 configured as monostable) would cause delay depending upon the values of R2 + C1.

b) After the delay, TIMER1 (555 configured as monostable) gets triggered thru C12. Then TIMER1 would power on PULSES1 (555 configured as astable) for a duration depending upon the values of R3 + C3.

c) PULSES1 would generate pulses depending upon the values of R4 + R5 + C10.

d) When the TIMER1 duration is completed, PULSES1 gets off and DELAY2 is triggered thru C13.

The lower 3 x 555 are almost copy of the upper 3 x 555.

e) DELAY2 causes a delay then triggers TIMER2.

f) TIMER2 switches on PULSES2, which generates pulses.

The outputs are V-Cyl, Dir, Pulse and H-Cyl, each have an LED connected thru a current limiting resistor.

Theoretically the circuit seems OK, simulation is also OK. But physically, I am facing some problems:

a) If TIMER2 is present, there will be no output at DELAY2. (H-Cyl LED doesn't light up).

b) if TIMER2 is removed, DELAY2 will give output and H-Cyl LED would light up. Interestingly, PULSES2 also generates pulses though without TIMER2.

The values of the timing components, in the simulator are changed for speeding up the results.

a) When a push button across C16 is pressed, DELAY1 (555 configured as monostable) would cause delay depending upon the values of R2 + C1.

b) After the delay, TIMER1 (555 configured as monostable) gets triggered thru C12. Then TIMER1 would power on PULSES1 (555 configured as astable) for a duration depending upon the values of R3 + C3.

c) PULSES1 would generate pulses depending upon the values of R4 + R5 + C10.

d) When the TIMER1 duration is completed, PULSES1 gets off and DELAY2 is triggered thru C13.

The lower 3 x 555 are almost copy of the upper 3 x 555.

e) DELAY2 causes a delay then triggers TIMER2.

f) TIMER2 switches on PULSES2, which generates pulses.

The outputs are V-Cyl, Dir, Pulse and H-Cyl, each have an LED connected thru a current limiting resistor.

Theoretically the circuit seems OK, simulation is also OK. But physically, I am facing some problems:

a) If TIMER2 is present, there will be no output at DELAY2. (H-Cyl LED doesn't light up).

b) if TIMER2 is removed, DELAY2 will give output and H-Cyl LED would light up. Interestingly, PULSES2 also generates pulses though without TIMER2.

The values of the timing components, in the simulator are changed for speeding up the results.