Follow along with the video below to see how to install our site as a web app on your home screen.

Note: This feature may not be available in some browsers.

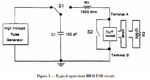

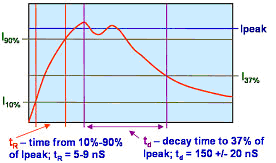

Are there test bench available (for example, with Human boday model, 2KV)with which the ESD protection circuit can be simulated?