ranilf

Newbie level 3

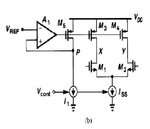

Hi I am designing a vco with replica biasing and have a few questions. For the design, I'm using a differential design as in the picture below. This was taken from Razavi's book. Now to the problems. I can't seem to get the replica bias to work properly, as the Vds value from the pmos in the replica bias never matches the load pmos in the diffamp. I have tried setting all the pmos in saturation and also all in linear but nothing seems to work. So here are a few questions:

1) Should the pmos be in linear region or can they be in saturation when acting as a resistor. Or do they have to be in deep triode region as the Razavi book says.

2) Also, any tips for biasing the transistors. I am using VDD = 3.3v and .35 micron technology

3) What is a good value for Vref to be.

4) Finally, should Iss and I1 be the same value, or should I1 be half the current of Iss since this is a half replica?

Thanks guys, and I would really appreciate any help as I've been stuck on this for a long time.

1) Should the pmos be in linear region or can they be in saturation when acting as a resistor. Or do they have to be in deep triode region as the Razavi book says.

2) Also, any tips for biasing the transistors. I am using VDD = 3.3v and .35 micron technology

3) What is a good value for Vref to be.

4) Finally, should Iss and I1 be the same value, or should I1 be half the current of Iss since this is a half replica?

Thanks guys, and I would really appreciate any help as I've been stuck on this for a long time.