xiangx93

Newbie level 6

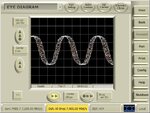

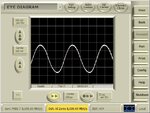

I've recently designed a wireline transmitter,but it turns out to have so much jitter.Since I can make sure that the clock generator is relatively clean,I think the noise most probably comes from some on-chip mechanism like IR-drop or inductor-induced jitter.So is there any way to approximate the IR&inductor's influence on circuits' performance?(Preferrably in Cadence)