deba_fire

Full Member level 3

Hi All,

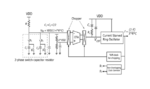

In the attached frequency locked loop, why is there a need of compensation network formed by Rz,Cz, and Cc? As far as I see there is only one integrator in the closed loop, the OTA. The oscillator from vctrl to output frequency is just a gain block since the output variable of interest is just frequency. Single integrator loops are inherently stable, so why is there a need of compensation?

Is there some small signal modelling which I am missing?

Thanks

In the attached frequency locked loop, why is there a need of compensation network formed by Rz,Cz, and Cc? As far as I see there is only one integrator in the closed loop, the OTA. The oscillator from vctrl to output frequency is just a gain block since the output variable of interest is just frequency. Single integrator loops are inherently stable, so why is there a need of compensation?

Is there some small signal modelling which I am missing?

Thanks