tiwari.sachin

Full Member level 6

I am using a DC to DC buck to convert 24V to 5V

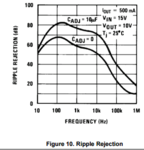

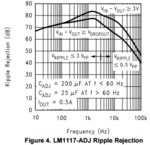

Followed by that a LM1117 to convert 5V to 3.3V

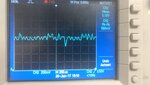

Although I am getting the required 5V and 3.3V but I see a lot of noise (ripples) at the output.

I am using 47uF Ceremic caps at 5V

and 10uF Ceramic caps with series 1R resistor at output of 3.3V

I did try to have more parallel caps but its not effecting much.

Any suggestions for how I can possibly reduce these ripples

- - - Updated - - -

The DC to DC operates at Fixed 570 kHz Switching Frequency

Followed by that a LM1117 to convert 5V to 3.3V

Although I am getting the required 5V and 3.3V but I see a lot of noise (ripples) at the output.

I am using 47uF Ceremic caps at 5V

and 10uF Ceramic caps with series 1R resistor at output of 3.3V

I did try to have more parallel caps but its not effecting much.

Any suggestions for how I can possibly reduce these ripples

- - - Updated - - -

The DC to DC operates at Fixed 570 kHz Switching Frequency