minhhoa2310

Newbie level 4

Sorry, I'm newbie. I have 3 problems that can not be solve more than 1 week. I need solve as soon as possible.

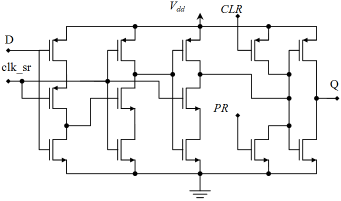

Firstly, please help me draw schematic in Cadence about D Flip Flop using NMOS and PMOS or something like these.

Secondly, please help me draw schematic 8-bit register with that D-FF.

Thirdly, please help me how I can connect PLL (Phased-Locked-Loop) with a 8-bit register which contains the input value to choose frequency in PLL ( Ex: when I choose 00000001, frequency is 50Hz; 00000010, frequency is 100Hz...)

Thank you very much.

Firstly, please help me draw schematic in Cadence about D Flip Flop using NMOS and PMOS or something like these.

Secondly, please help me draw schematic 8-bit register with that D-FF.

Thirdly, please help me how I can connect PLL (Phased-Locked-Loop) with a 8-bit register which contains the input value to choose frequency in PLL ( Ex: when I choose 00000001, frequency is 50Hz; 00000010, frequency is 100Hz...)

Thank you very much.