lolxiang

Newbie level 1

Hi all

I was designing a peak detector with cadence. I used a very simple structure as shown in the first figure, an op amp drives a MOS diode to charge a hold cap, and feedback ensures the output tracks the input when input is higher.

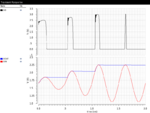

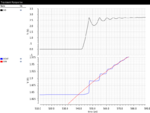

The simulated waveform are as in p1 and p2 where some kind of oscillation is found. The op amp is unity-gain stable with that hold cap, but when I replaced the op amp with an ideal model the oscillation is gone. So I think it is due to the instability of the feedback, but with that diode I have no ideal how to tackle this problem. Any advice is appreciated.

I was designing a peak detector with cadence. I used a very simple structure as shown in the first figure, an op amp drives a MOS diode to charge a hold cap, and feedback ensures the output tracks the input when input is higher.

The simulated waveform are as in p1 and p2 where some kind of oscillation is found. The op amp is unity-gain stable with that hold cap, but when I replaced the op amp with an ideal model the oscillation is gone. So I think it is due to the instability of the feedback, but with that diode I have no ideal how to tackle this problem. Any advice is appreciated.