redsees

Junior Member level 1

Hello World,

I'm new into the world of Digital Design using FPGA's and PLD's generally.

I was designing a simple code in verilog that does a few bits permutations, when I tested it, always the least significant two bits are x's, I don't know why?

Here is my Verilog code:

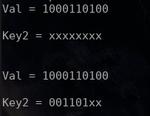

The output is always:

The first case is okay, but the problem in the second one, why is the least significant 2 bits are always double x's?

I'm new into the world of Digital Design using FPGA's and PLD's generally.

I was designing a simple code in verilog that does a few bits permutations, when I tested it, always the least significant two bits are x's, I don't know why?

Here is my Verilog code:

Code:

module Generate_Keys(input[0:9] key, input clk, output[0:7] key2);

reg[0:9] p10_out;

reg[0:7] tempC, tempD;

always@(posedge clk)

begin

// Some permutations

p10_out = {key[2], key[4], key[1], key[6], key[3], key[9], key[0], key[8], key[7], key[5]};

// Left Rotation by 3 bits

tempC = {p10_out[3:4], p10_out[0:2], p10_out[8:9], p10_out[5:7]};

// More permutations

tempD = {tempC[5], tempC[2], tempC[6], tempC[3], tempC[7], tempC[4], tempC[9], tempC[8]};

end

assign key2 = tempD;

endmodule

module tb;

reg clk = 1'b0;

reg[0:9] key;

wire[0:7] key2;

always

#5 clk = ~clk;

initial

$monitor("Val = %b\n\nKey2 = %b\n\n",key, key2);

initial

begin

key = 10'b1000110100;

#100;

$finish;

end

Generate_Keys inst0 (.key(key), .clk(clk), .key2(key2));

endmoduleThe output is always:

The first case is okay, but the problem in the second one, why is the least significant 2 bits are always double x's?