velu.plg

Member level 5

FPGA info: virtex7 , xc7v200t . Is virtex7 FPGA Supports MIPS processor Soft IP. If it's supports the corresponding FPGA means what us the maximum achachievable frequency.And which MIPS series optimized for FPGA?

Follow along with the video below to see how to install our site as a web app on your home screen.

Note: This feature may not be available in some browsers.

you know what a soft IP is, right? any FPGA can take it, as long as there are resources.

you know what a soft IP is, right? any FPGA can take it, as long as there are resources.

Sure,but we can't achieve same clock frequency as such in ASIC. If you already tried this above scenario means tell me the maximum achievable clock frequency.

not funny! I think you don't have experience in that domain. thanks for your responseSure, I will consult my favourite palm reader and let you know what the max freq is.

not funny! I think you don't have experience in that domain. thanks for your response

not funny! I think you don't have experience in that domain. thanks for your response

On the other hand, YOU seem to have heaps of... wait, no. You don't. Let's recap what you just asked.

---cut---

Have you ever programmed an FPGA, ever? There is this magical thing called RTL that you can transform into circuits!

The xc7v200t is the largest FPGA at the moment, and it is very inconvenient to work with it (I had the experience. It is very expensive, consumes large current and so on.

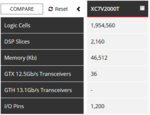

I noticed that and was too lazy to point it out.There's actually no xc7v200t, xc7v2000t is the largest Virtex 7 and - expensive enough - to be used only for very special applications like ASIC prototyping.