ktx2222

Member level 5

Hi all,

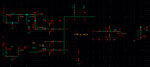

I have design a double balanced Gilbert cell mixer.

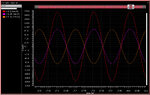

In ADS, the output IFp and IFn are 180 deg out of phase.

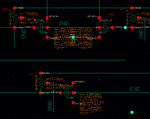

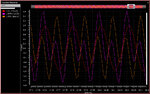

Then I simulate in Cadence, the problem is that the IFp and IFn signals are in phase. I think that is the reason why the conversion gain is smaller than 0 dB.

I have spent couple of days but I cannot figure out the reason. Please help! Thank you so much.

I have design a double balanced Gilbert cell mixer.

In ADS, the output IFp and IFn are 180 deg out of phase.

Then I simulate in Cadence, the problem is that the IFp and IFn signals are in phase. I think that is the reason why the conversion gain is smaller than 0 dB.

I have spent couple of days but I cannot figure out the reason. Please help! Thank you so much.