Alper özel

Member level 1

- Joined

- Feb 28, 2015

- Messages

- 40

- Helped

- 0

- Reputation

- 0

- Reaction score

- 0

- Trophy points

- 6

- Location

- Turkey / Scotland

- Activity points

- 487

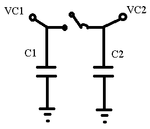

I need to design a system that equalizes the two capacitors on each side. There are two big capacitors in the system and they will be charging and discharging by out of the system. They might reach to 105V and down to GND at any time. We won't know that, I am only responsible for equalizing the capacitor voltages by an interrupt input.

For simplicity I draw the figure above. VC1 and VC2 may have the voltage level of 0 to 105 sererately at any time!

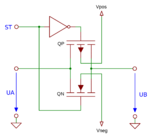

The thing is, I can not consume much power, I have to be efficient. So selenoid and other inefficient switching solutions don't work here. I would use transmission gates(like in the figure below) to do it if capacitor potentials were not allowed to exceed 20V (Due to VGSVGS limitations) but it is not a fit for this system either. So, is there any energy efficient method to allow bilateral current transmission? (In OPEN State there will be no current flow, in CLOSED State Current will flow from high potential to the lower potential)

Thanks in advance.

For simplicity I draw the figure above. VC1 and VC2 may have the voltage level of 0 to 105 sererately at any time!

The thing is, I can not consume much power, I have to be efficient. So selenoid and other inefficient switching solutions don't work here. I would use transmission gates(like in the figure below) to do it if capacitor potentials were not allowed to exceed 20V (Due to VGSVGS limitations) but it is not a fit for this system either. So, is there any energy efficient method to allow bilateral current transmission? (In OPEN State there will be no current flow, in CLOSED State Current will flow from high potential to the lower potential)

Thanks in advance.